0x00 前言

笔者在本系列文章的第一篇中,提出了几个目标,现在还剩下「设计 PCB 并打样验证」未实现。本文是 RP2040 学习笔记的完结篇,在本文中,我们将参考树莓派官方指引,设计 pcb 板。

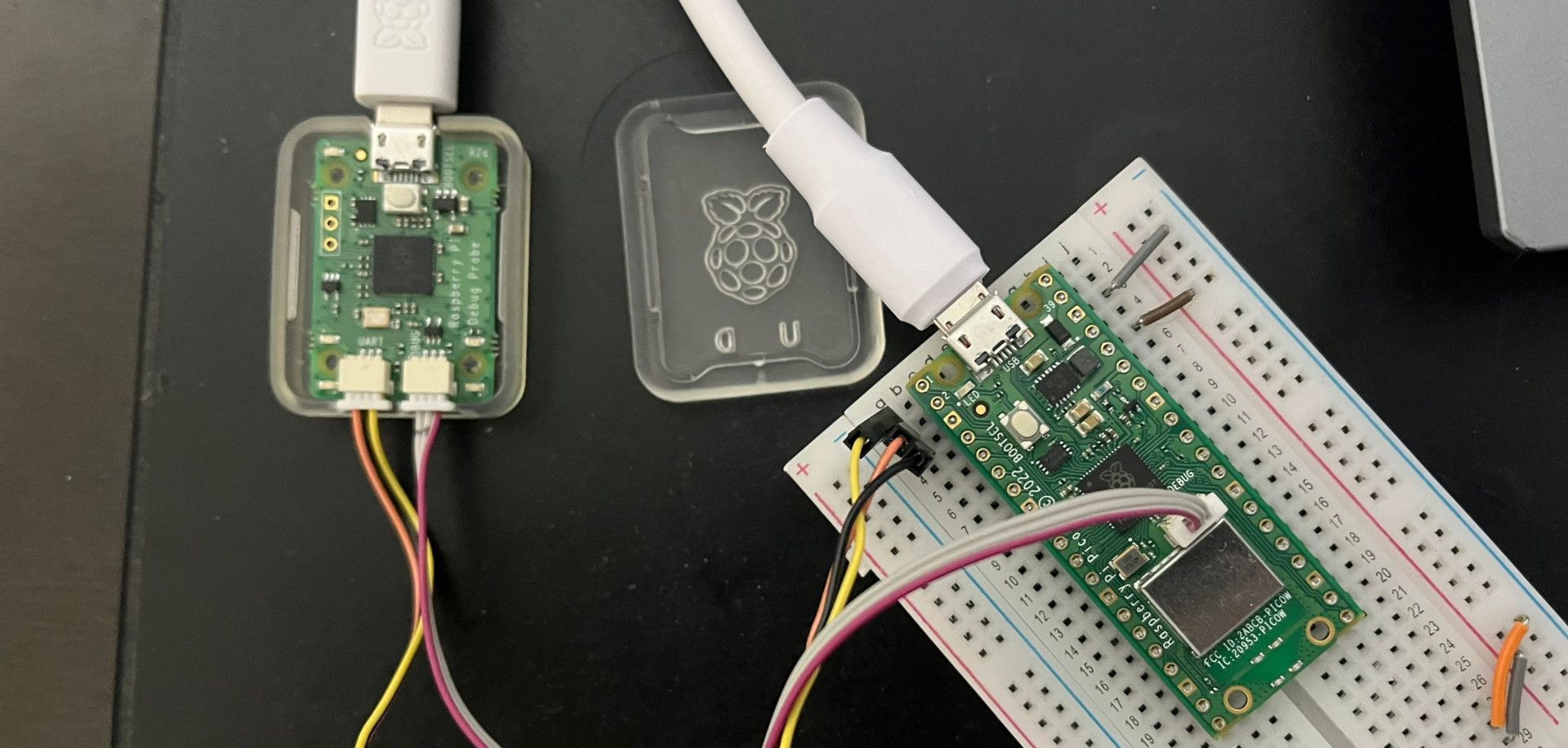

目前,我们要在 Pico 上进行开发,则需要从 debug probe 引出 SWD 线和 UART 线,如下图所示。SWD 线暂且好说,但 UART 线容易接错端口。如果使用的不是 Pico H 而是 Pico,则需要连 6 条杜邦线(SWDIO、SWCLK、GND、串口 TX、串口 RX、串口 GND)。另外,我们需要通过两条 USB 线给 debug probe 和 Pico 供电。总而言之,线路比较复杂。

因此,本文来设计一套线路更简洁的开发板。具体而言:

- 从调试器引出 5V 供电、SWD、串口;

- 上述接口通过软排线连接到开发板,因此在常规开发时,开发板无需另接串口、SWD、电源线;

- 开发板上提供 type c 接口,以提供 usb 1.1 连接(例如 MicroPython 所用的 usb 虚拟串口);

- 开发板上提供 reset 按钮。

在动手画板子之前,我们先阅读树莓派文档,然后看看开源社区是如何为 RP2040 设计 PCB 的。

0x01 阅读手册

树莓派提供了《Hardware design with RP2040》手册,以指引 RP2040 PCB 设计。手册给出了一个最小系统板设计,以及一个带有 VGA、SD 卡、音频接口的设计。本文主要参考最小系统板。

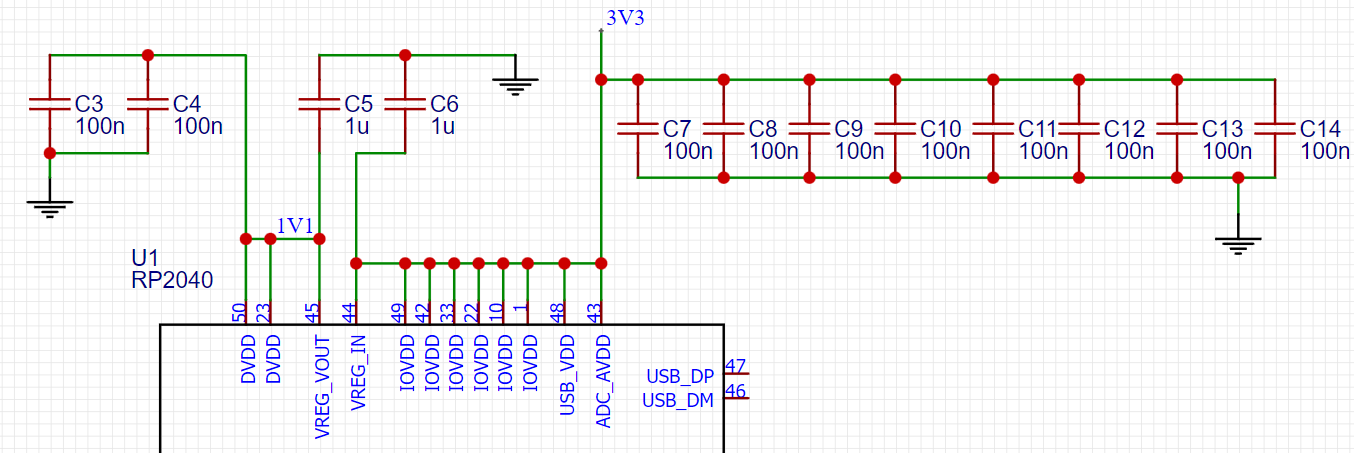

RP2040 的 PCB 设计可以分为四个组件:电源、flash、晶振、IO。我们来观察手册中给出的参考设计。

电源

根据 datasheet,RP2040 需要以下几种电源:

- IOVDD(digital IO supply)用于 IO,需要 1.8~3.3V。每个 IOVDD 引脚应该连接 100nF 去耦电容。

- DVDD(digital core supply)是核心电压,需要 1.1V。每个 DVDD 引脚应该连接 100nF 去耦电容。

RP2040 内置了降压电路,将 VREG_VIN 降压到 1.1V 输出至 VREG_VOUT 引脚。因此,我们无需从外部供应 1.1V 电压,只需给 VREG_VIN 提供 3.3V 电压、并将 VREG_VOUT 连接到 DVDD。 - VREG_VIN 作用如上所述,它应该连接 1uF 电容。

- USB_VDD 用于给 USB PHY 供能,需要 3.3V。它应该连接 100nF 去耦电容。

- ADC_AVDD 用于给 ADC 供能,需要 1.8~3.3V。它应该连接 100nF 去耦电容。

综上所述,对于最小系统,只需把 VREG_VOUT 和 DVDD 直连起来,然后给其他的电源输入引脚提供 3.3V 电压。这 3.3V 电压可以从 usb 线输出的 5V 电压通过 LDO 降压获得。

现在来看最小系统板的设计。

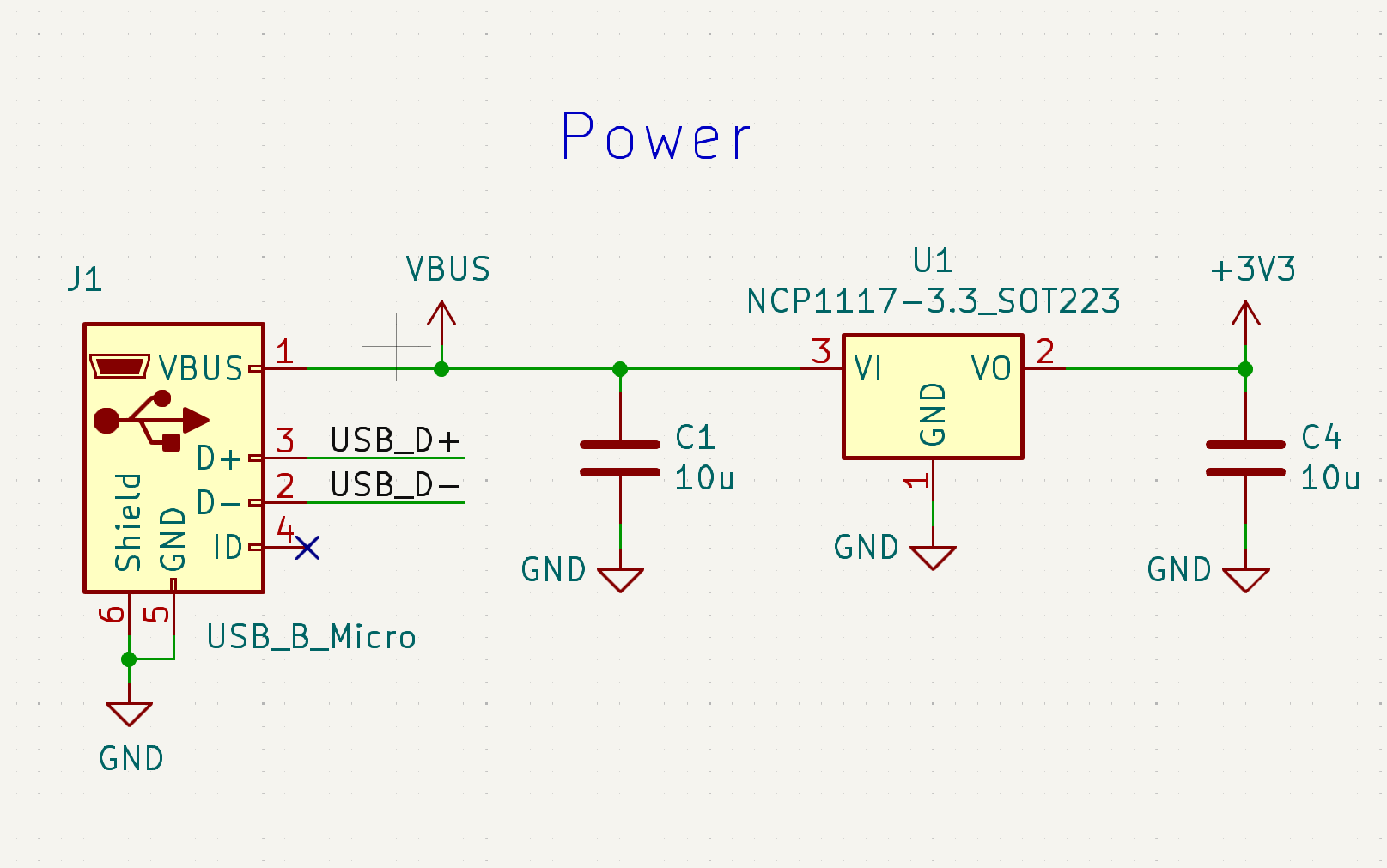

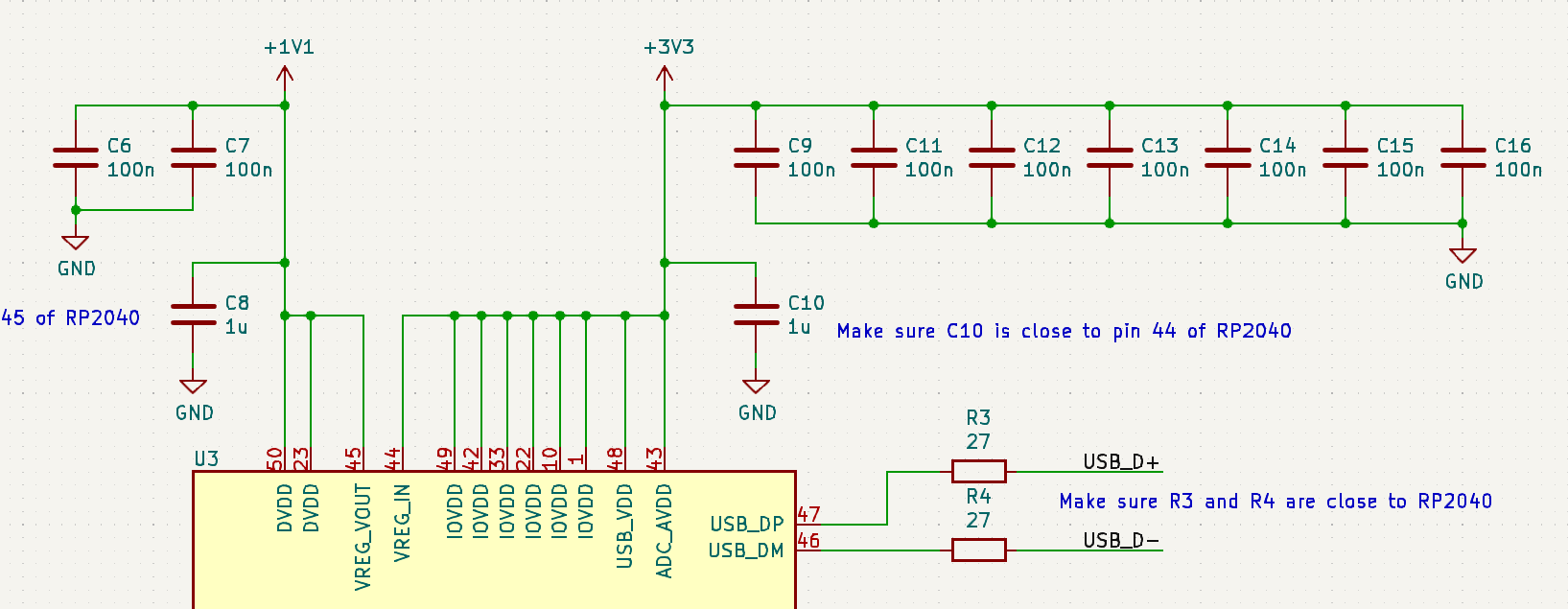

最小系统板从 usb 引出 5V 的 VBUS,用 10uF 电容滤波,输出到 LDO 芯片,产生 3.3V 电压,输出的 3V3 也要连接 10uF 滤波电容。而 RP2040 芯片的 VREG_VOUT 连接到 DVDD,其余电源输入连接 3V3。注意 VREG_IN 和 VREG_VOUT 必须各连接 1uF 的滤波电容。

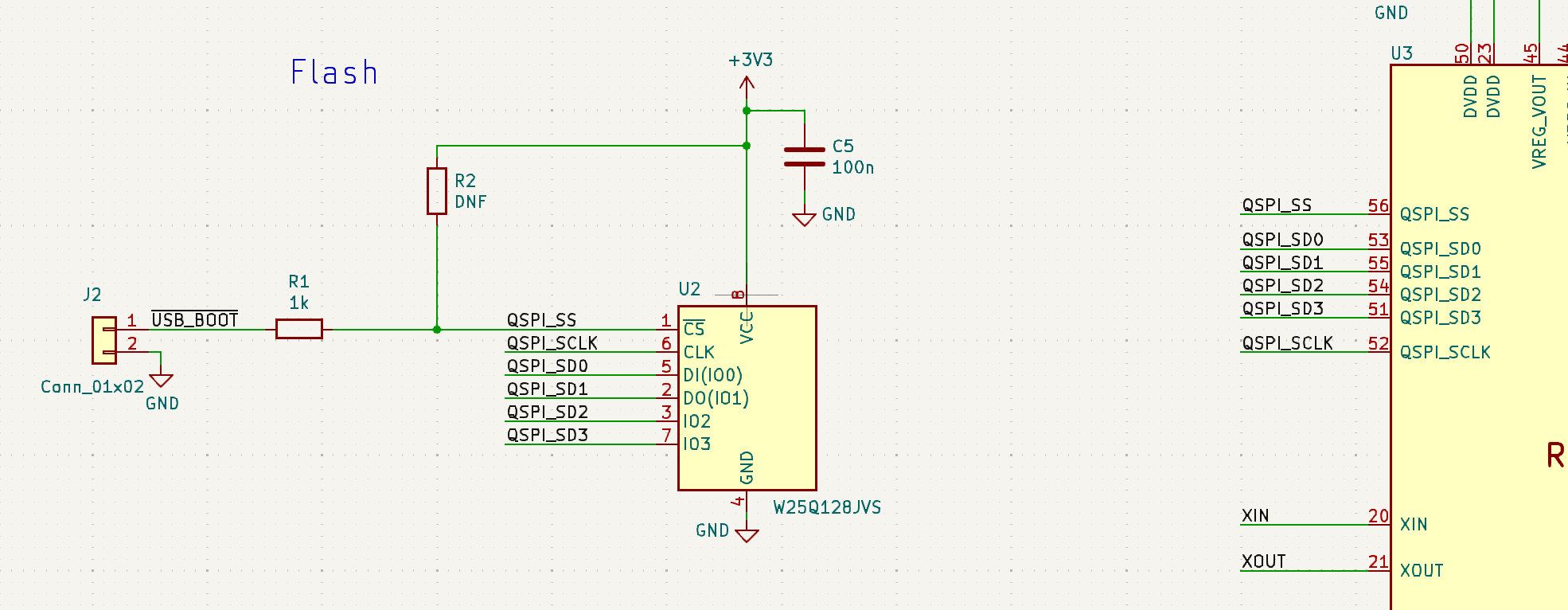

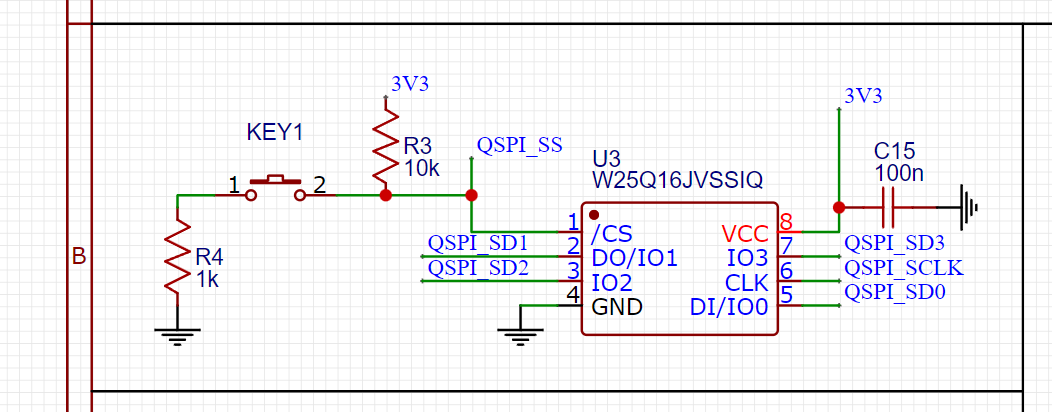

flash

最小系统板选用 W25Q128JVS 作为 flash 芯片,有主线 openocd 支持。电路如下:

最左侧即为 bootsel,在 Pico 板上是按钮,在这个板上是排针,用跳线帽可以接地。启动阶段,若 QSPI_SS 接地,则进入 usb 下载流程;否则正常启动。

RP2040 启动时会自动拉高 QSPI_SS 引脚,但有一小段时间中 QSPI_SS 的状态不好保证。R2 这个 10k 电阻是用来上拉 QSPI_SS 的,从而在这段不保证 QSPI_SS 的时间内也能正常工作。不过,实验发现,对于这个 flash,就算没有这个 R2 也没问题,所以可以不焊接。但针对其他 flash 芯片,焊接 R2 比较保险。

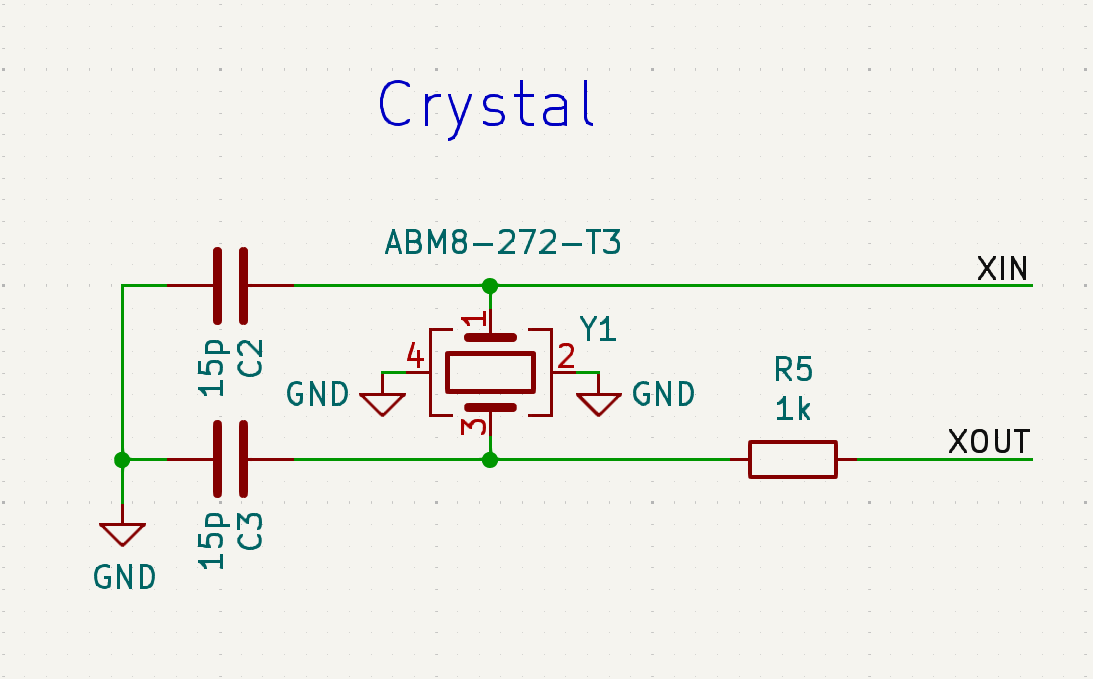

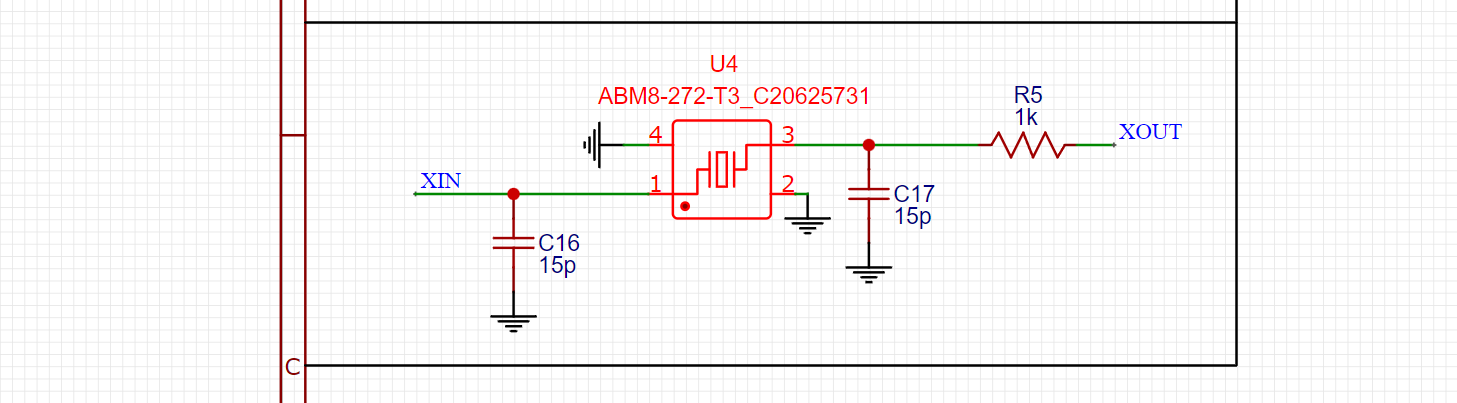

晶振

最小系统板的晶振电路设计如下:

有两种方式给 RP2040 提供时钟信号:要么给 XIN 引脚提供方波,要么在 XIN 和 XOUT 之间连接 12MHz 晶振。树莓派文档中推荐采用 ABM8-272-T3 晶振,使用 15pF 的匹配电容。我们自己的 PCB 设计可以沿用这套晶振电路。

IO

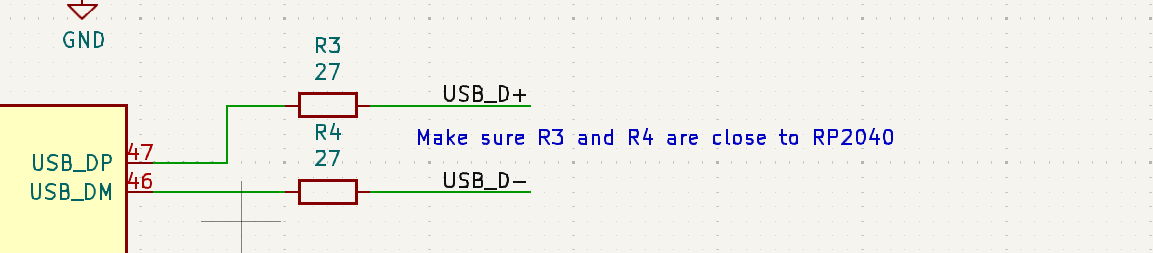

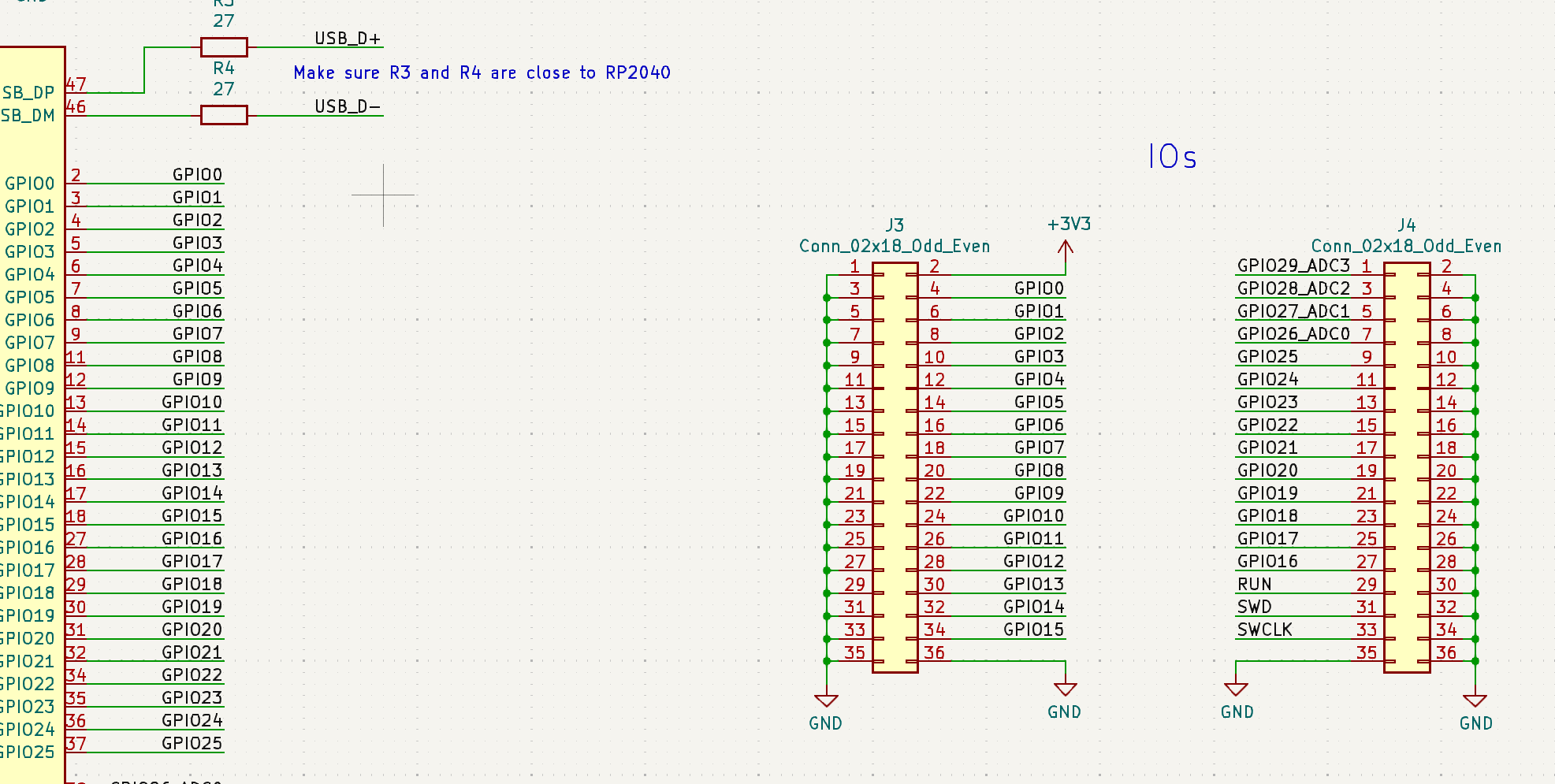

最后来讨论 IO 电路设计。首先,对于 usb 信号,最小系统板的设计如下:

这里给 D+、D- 信号串联了 27ohm 的电阻,以符合 usb 规范。另外,usb 信号线下方应当铺铜。

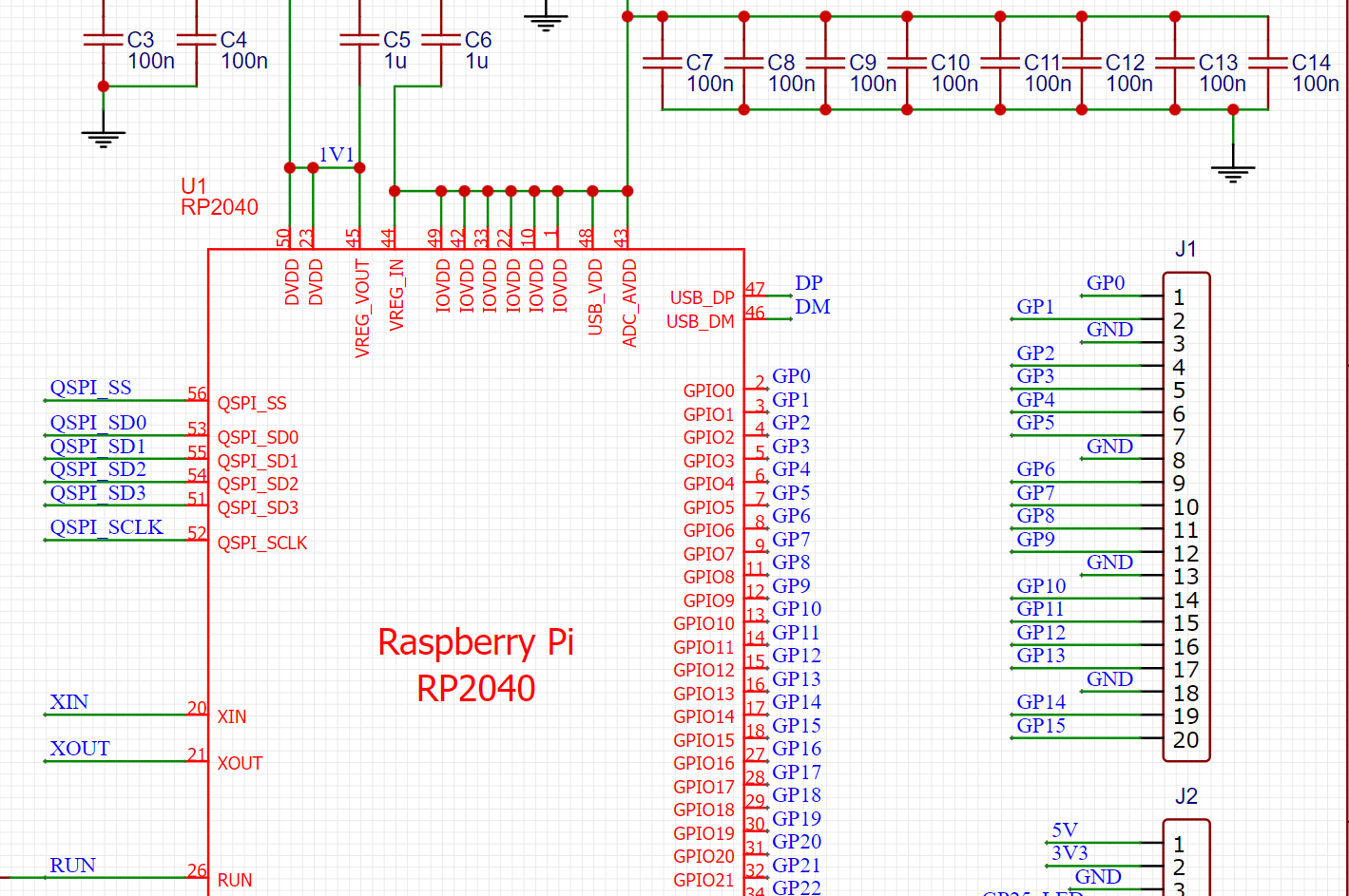

其他 GPIO 引出到排针:

至此,我们分析完了最小系统板的 PCB。

0x02 开源社区中的 RP2040 PCB 设计

下面看看其他开源 PCB 与官方最小系统板的区别。

树莓派 Pico

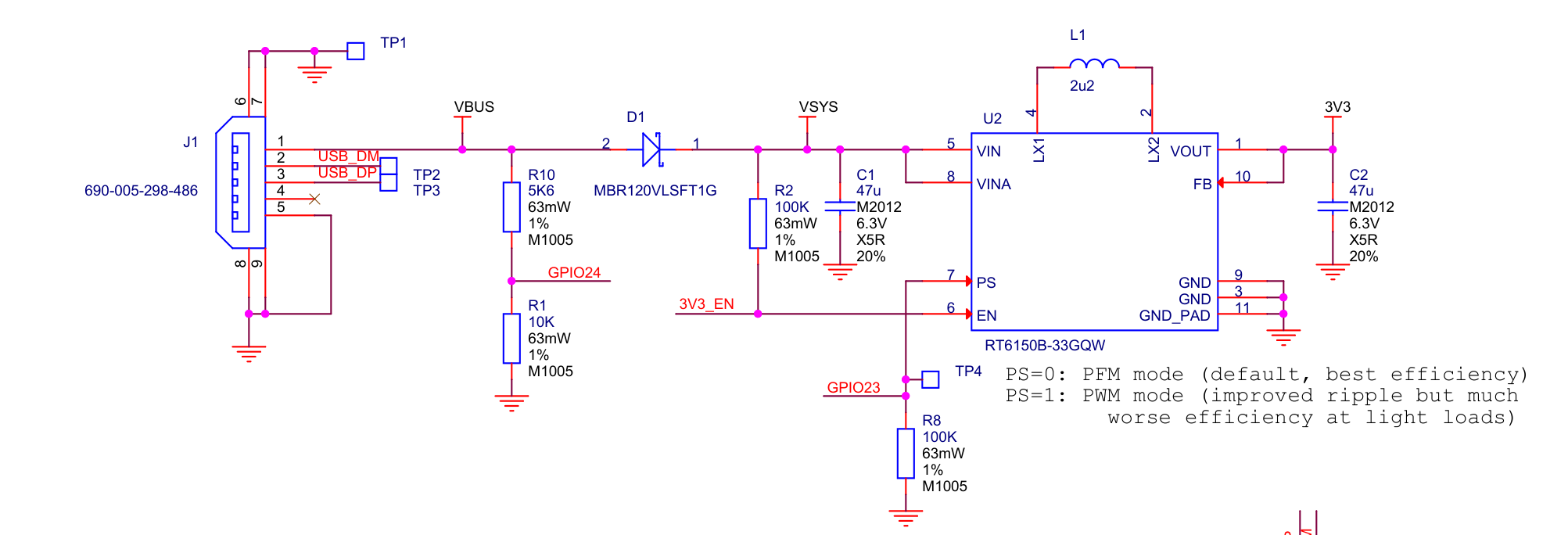

Pico 板的 PCB 是开源的,其供电设计与最小系统板很不一样,如下图:

它使用了 buck-boost 电路来输出 3V3,使得电源供应可以在 1.8V~5.5V 之间。我们的应用无需如此宽的电压范围,所以不必采用这种设计。

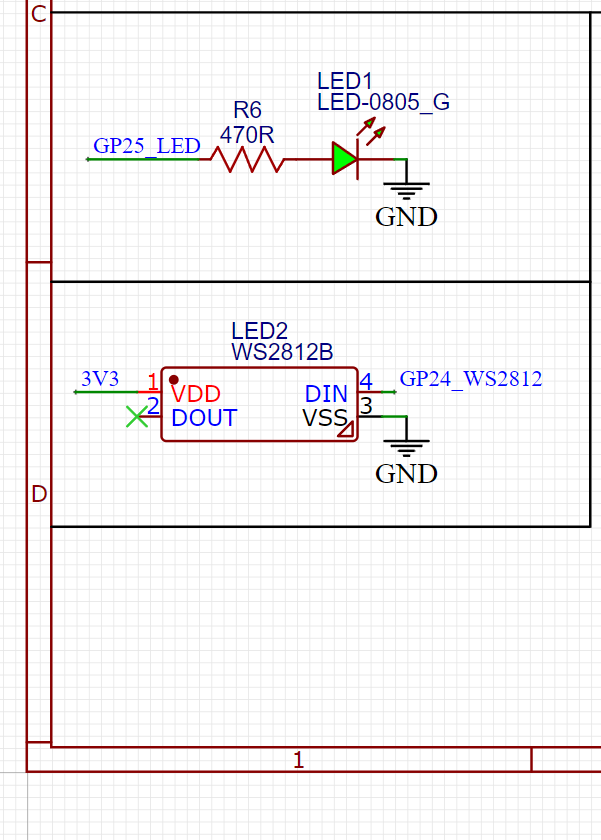

Pico 将 GPIO25 连接到了 LED,其间串联一个 470ohm 的限流电阻。ADC_AVDD 不是直连 3V3,而是在其间串联了两个电阻。兼容 Pico 引脚设定的开发板大多沿用了这两个电阻。

其他组件与最小系统板无甚差别。

合宙 RP2040 开发板

笔者手头有几个购于 2023 年的合宙 RP2040 开发板,没想到现在价格翻了十倍(笑)。这个 PCB 也是开源的,我们来分析一下。

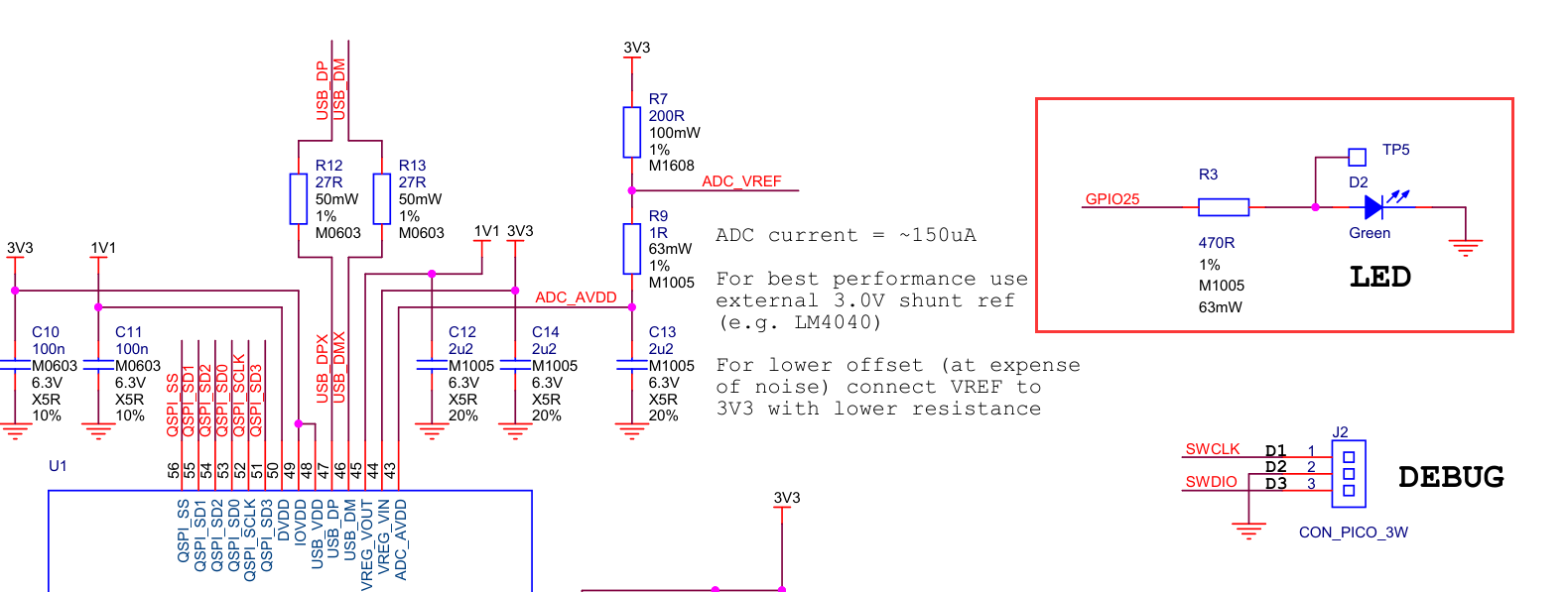

flash 芯片采用了 W25Q128JVS(实际货品上则未必),用 R7 电阻上拉 QSPI_SS。另外,LDO 芯片选用 SGM2019。

微雪 RP2040-Zero 开发板

微雪电子的 Zero 开发板是开源的,面积非常小,边缘为邮票孔,但两面都有元件,不适宜作为模组焊接到其他 PCB 上。先来看供电:

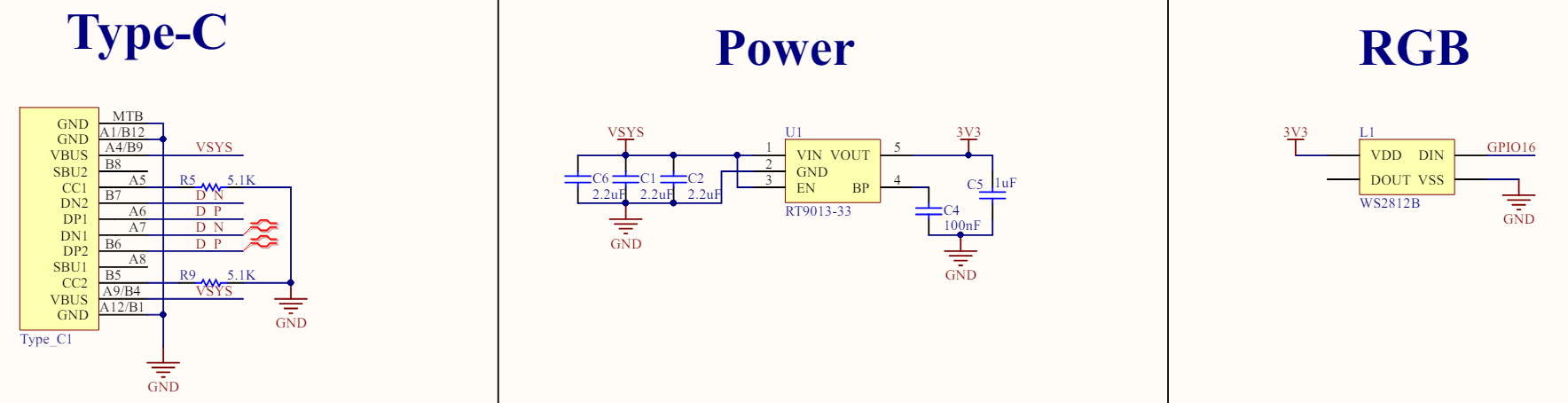

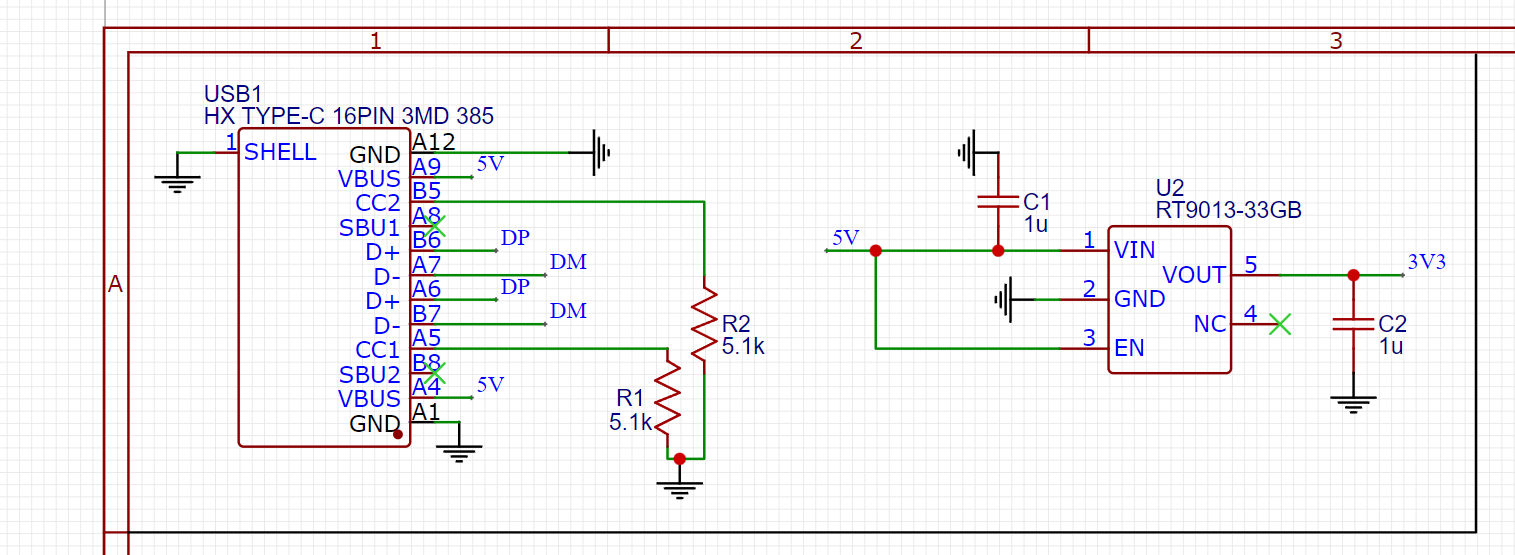

微雪 Zero 开发板使用的 LDO 是 RT9013-33。另外,type c 接口这边,CC 线通过 5.1k 电阻接地,具体意义可以参考 USB 中文网的文章。

flash 芯片选用与官方 Pico 板一致的 W25Q16JV,没有用电阻拉高 QSPI_SS 引脚。Zero 开发板提供了复位按钮,按下后 RUN 引脚接地,芯片复位。

微雪 RP2040-Tiny 开发板

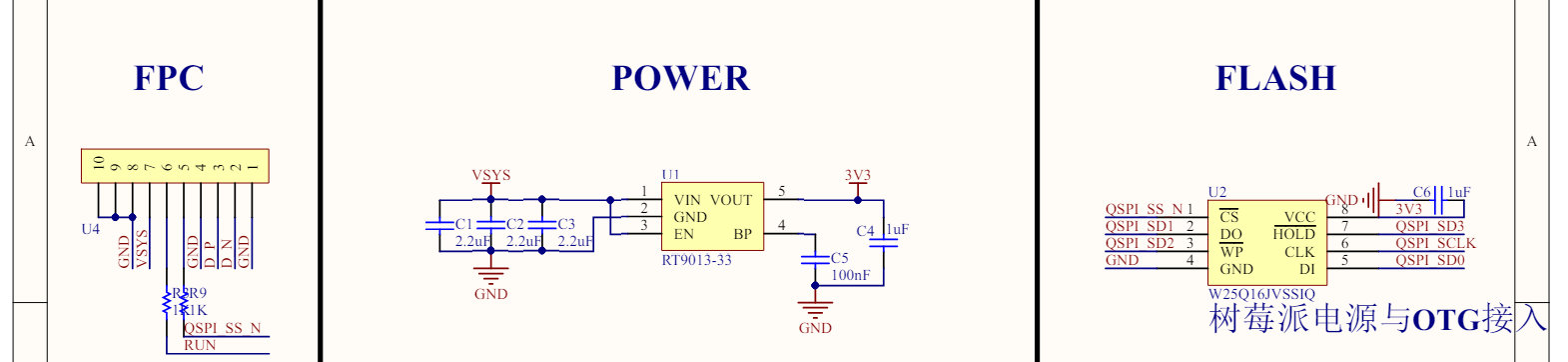

Tiny 开发板比较接近笔者文章一开头提出的连接方式。Tiny 板上并没有 usb 插座,取而代之的是软排线端口。排线传递 usb 和 bootsel、run 信号,没有 swd 信号,有点遗憾。

除了 FPC 软排线之外,其他设计与 Zero 开发板基本一致。

微雪 RP2040-One 开发板

One 开发板的特色是可以直插电脑的 usb 端口,无需线缆。其 PCB 设计也是最简单的。

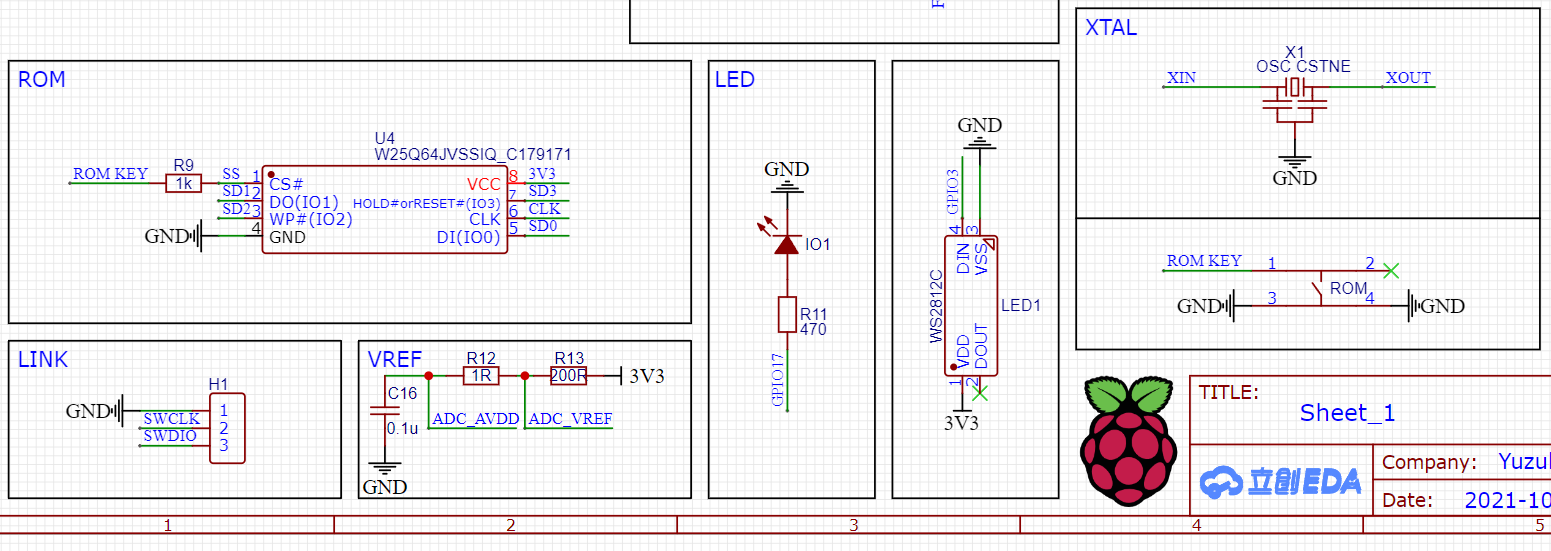

YuzukiCore Pico RP2040 核心板

看一份来自 DIY 玩家的方案:YuzukiCore 核心板。它被设计为 M.2 2230 的形状,以便作为模块插到其他 PCB 板上。先看 flash 和晶振电路:

YuzukiCore 采用的 flash 是 W25Q64JV,大小为 8MB。晶振是陶瓷晶振,据评论区所言,精度较低,建议换成石英晶振。其他设计与最小系统板相似。

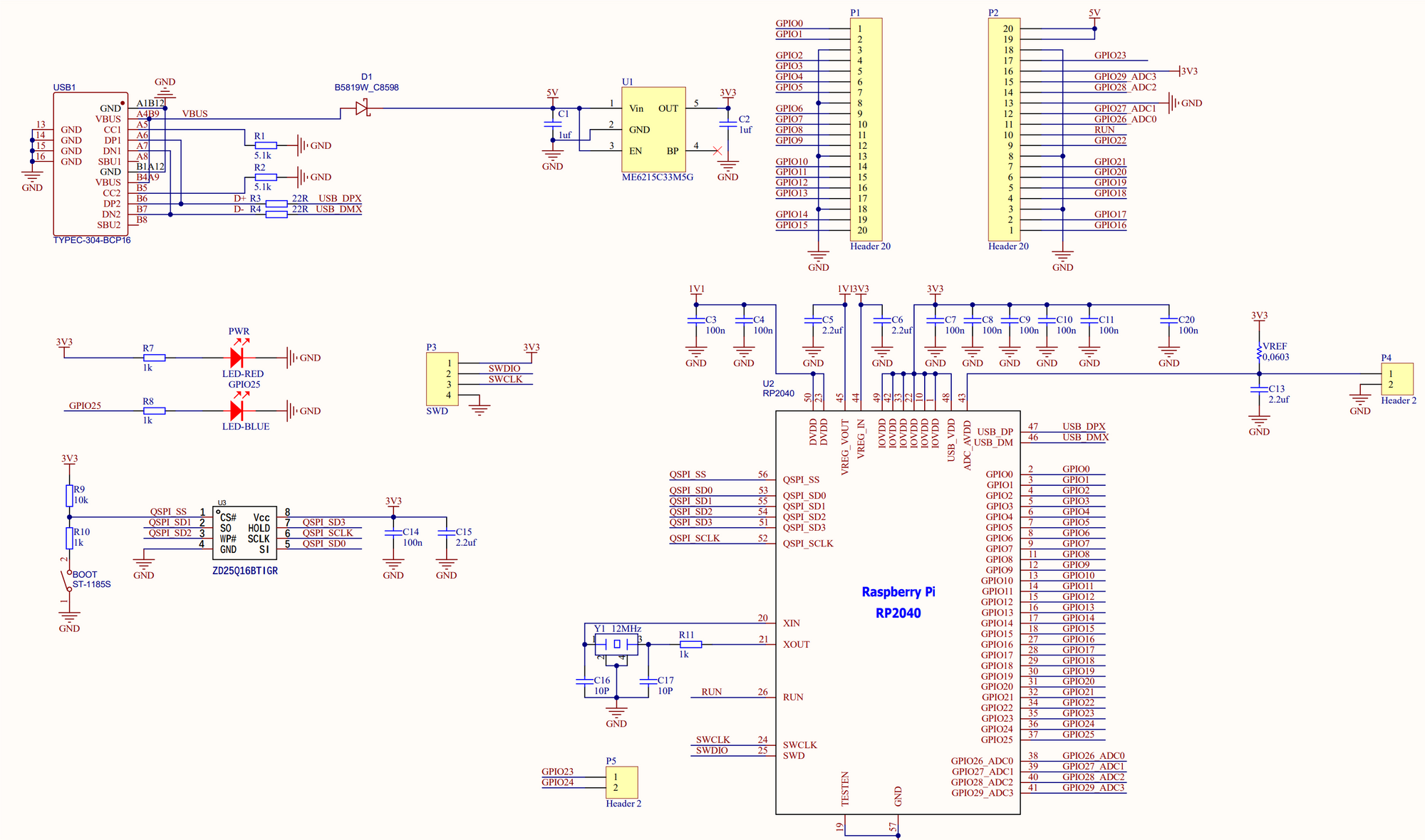

源地工作室 YD-RP2040-Lite

源地工作室设计了两块 RP2040 开发板,其中 Lite 开发板的资料在 github 上。它兼容 Pico 引脚布局,把 DCDC 改成了 LDO,micro usb 改成 type c。原理图:

原理图中没有标注晶振型号,从实物上可以看到采用了 YXC 的产品。 flash 改成了 ZD25Q16BTIGR,它的最高频率是 120MHz,低于 W25Q16JV 的 133MHz。如此选型大概是出于成本考虑(以立创商城为例,ZD25Q16BTIGR 大批量订货的单价是 0.7103 CNY,W25Q16JVSSIQ 则是 0.9439 CNY),但考虑到零售端 W25Q16JV 更容易买到,我们 DIY 玩家应该选择 W25Q16JV。

电源方面,此开发板将 usb 电压接了一个肖特基二极管,再接到 LDO(选用 ME6215)。这个肖特基二极管的用途是防电流倒灌。实测这个二极管带来了 0.28V 的压降,导致开发板的 5V 输出引脚实际上只有 4.77V。

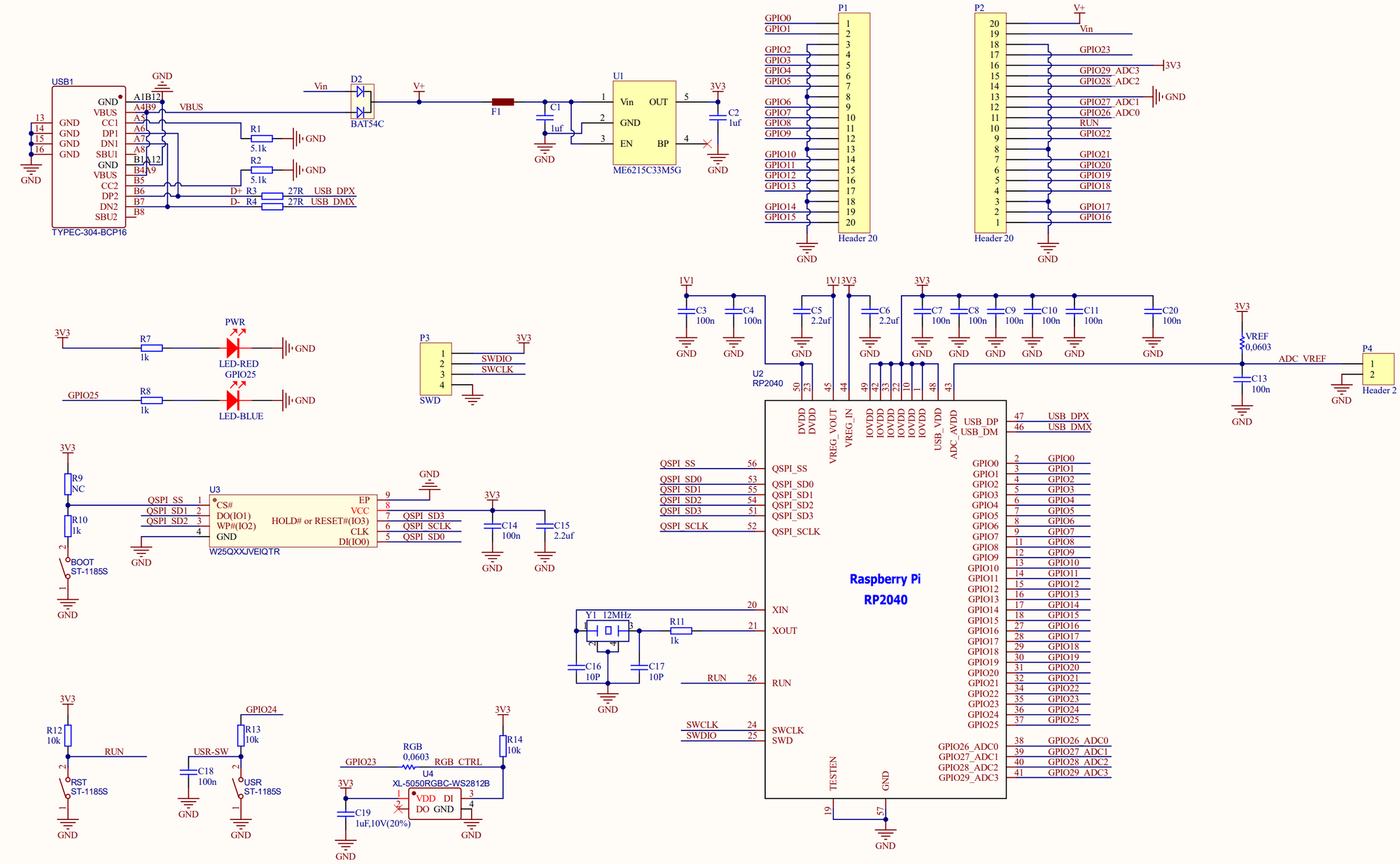

源地工作室 YD-RP2040

源地的 Lite 开发板(8.9 CNY)是极致省料,非 Lite 版本(10.5 CNY)则有了很多改进:

- flash 换回华邦的产品。4MB 开发板上搭载的是 W25Q32JV。

- 有 usb 和 Vin 两个电源输入,它们连接到肖特基二极管后,经过自恢复保险丝,连接 LDO。

- GP23 连接到 ws2812 LED。用户可以摘掉 0 欧电阻,以断开连接。

- GP24 连接到按钮。提供了消抖电容。

原理图:

0x03 设计开发板

我们已经看过了许多开发板,现在总结一下自己开发板的需求:

- 提供 type c 母座

- 提供 reset 按键

- GP25 接到 led,同时提供 ws2812b(用 pico 未引出的引脚实现)

- 采用 W25Q16JV 以提供最好的兼容性

- 预留 swd 口以备不时之需

- 为方便手焊,阻容采用 0603 封装,flash 采用 SOIC8 封装

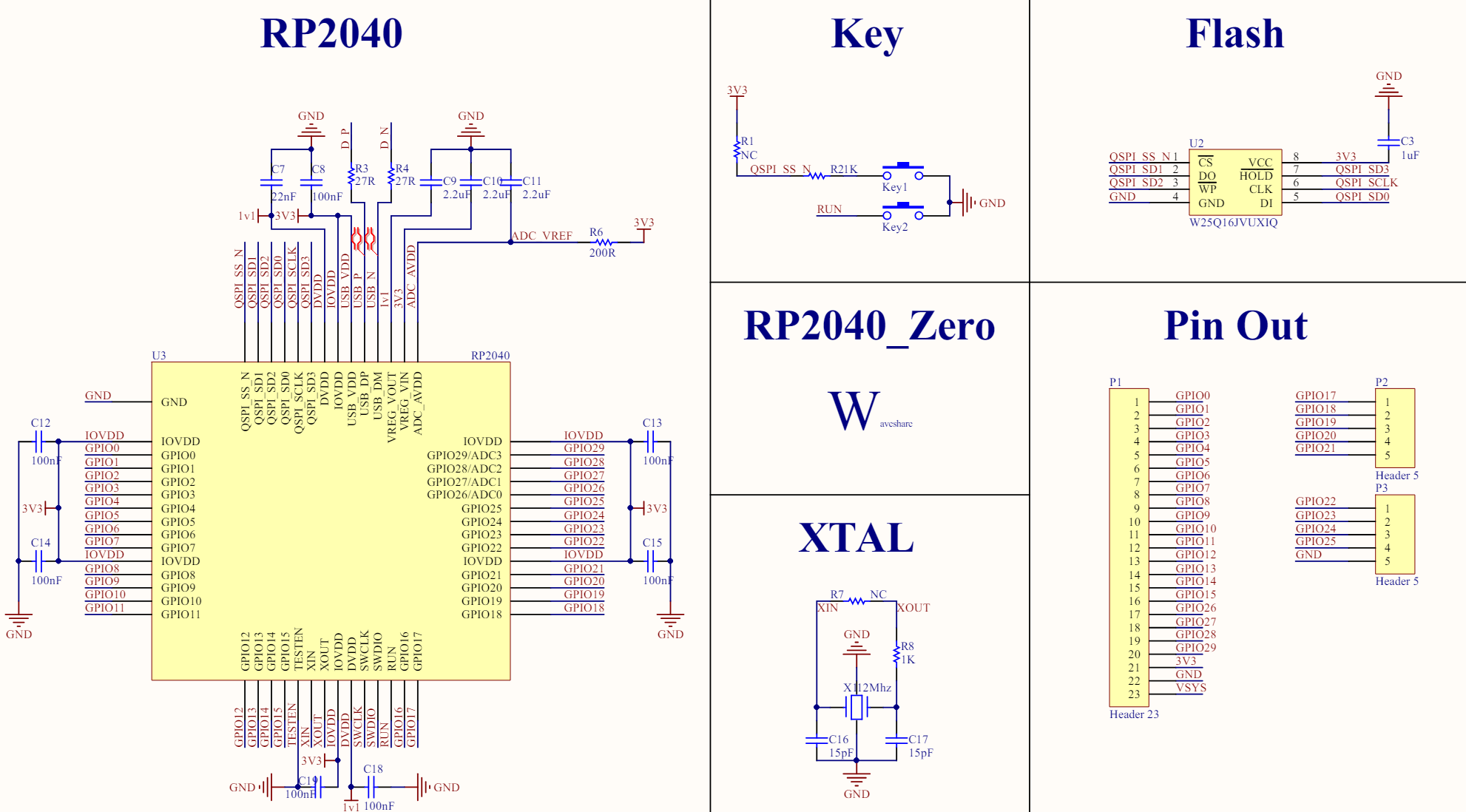

现在便开始设计。首先考虑电源电路,我们通过 type c 接入 5V 电压,由 LDO 分压到 3.3V。LDO 选用与微雪一致的 RT9013,按照手册,VIN 和 VOUT 各接 1uF 电容即可。由此设计出电源输入:

现在将 3.3V 电源连接到 RP2040 上。按照手册,VREG_IN 和 VREG_VOUT 连接 1uF 滤波电容,其余电源引脚连接 100nF 去耦电容。设计如下:

接下来考虑 flash 电路。W25Q16JV 系列 flash 有多种型号,封装不同,我们选择 SOIC8 封装的 W25Q16JVSSIQ。保险起见,我们用 10k 电阻上拉 QSPI_SS。

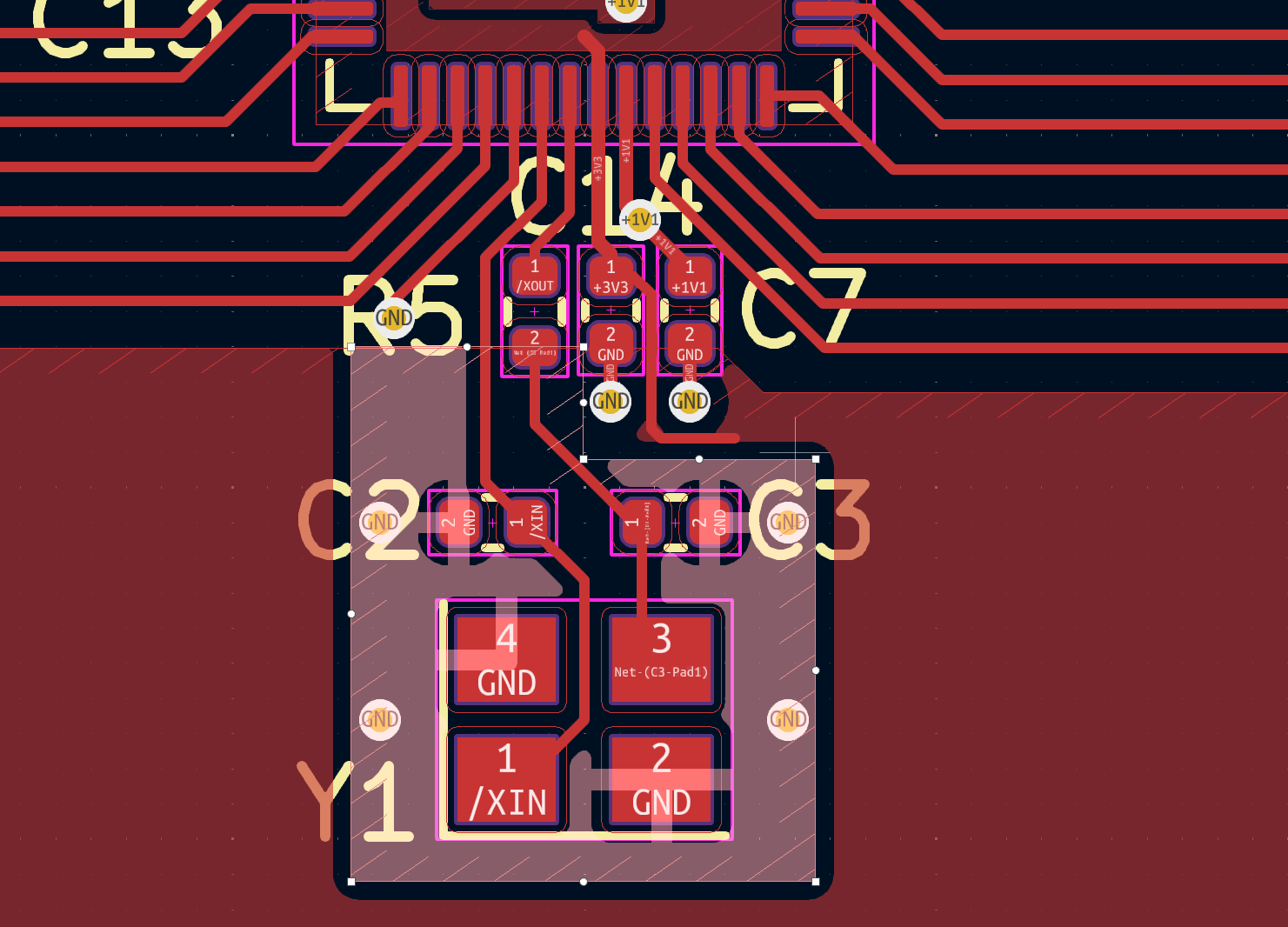

接下来是晶振电路。我们沿用最小系统板的 ABM8-272-T3 晶振,匹配电容 15pF。

最后是 IO 电路。我们要引出 GPIO、引出 SWD、提供 LED 和 WS2812B。

Pico 引出了 GP0~22、GP26~28,而 GP25 连接 LED。Pico W 的 GPIO 引出情况与之一致,不过 GP23~25 和 GP29 被用于连接无线 SoC。我们选择把 GP25 连接到 LED,GP24 连接到 WS2812B,按照 Pico 的方式引出 GPIO。

合影:

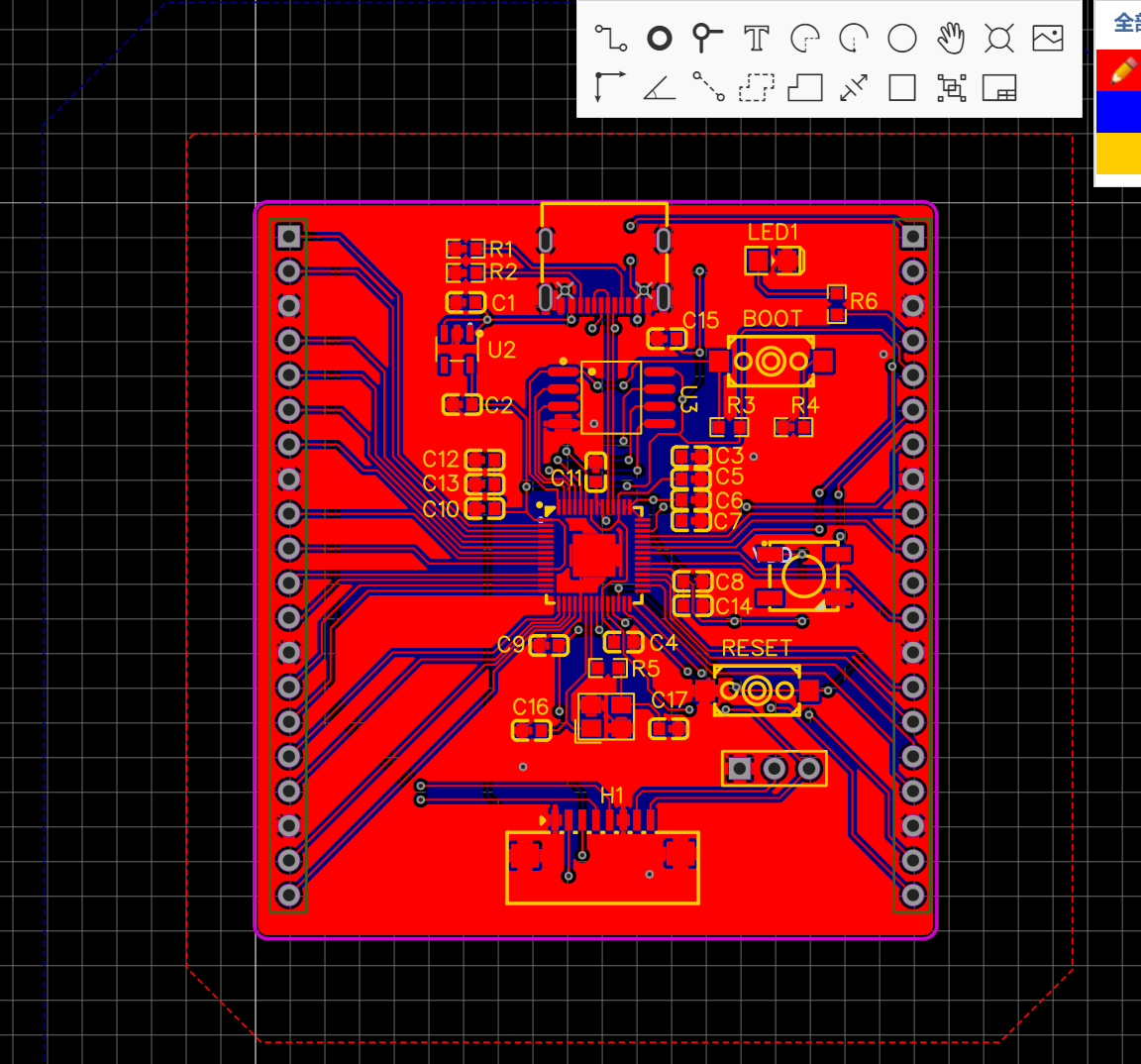

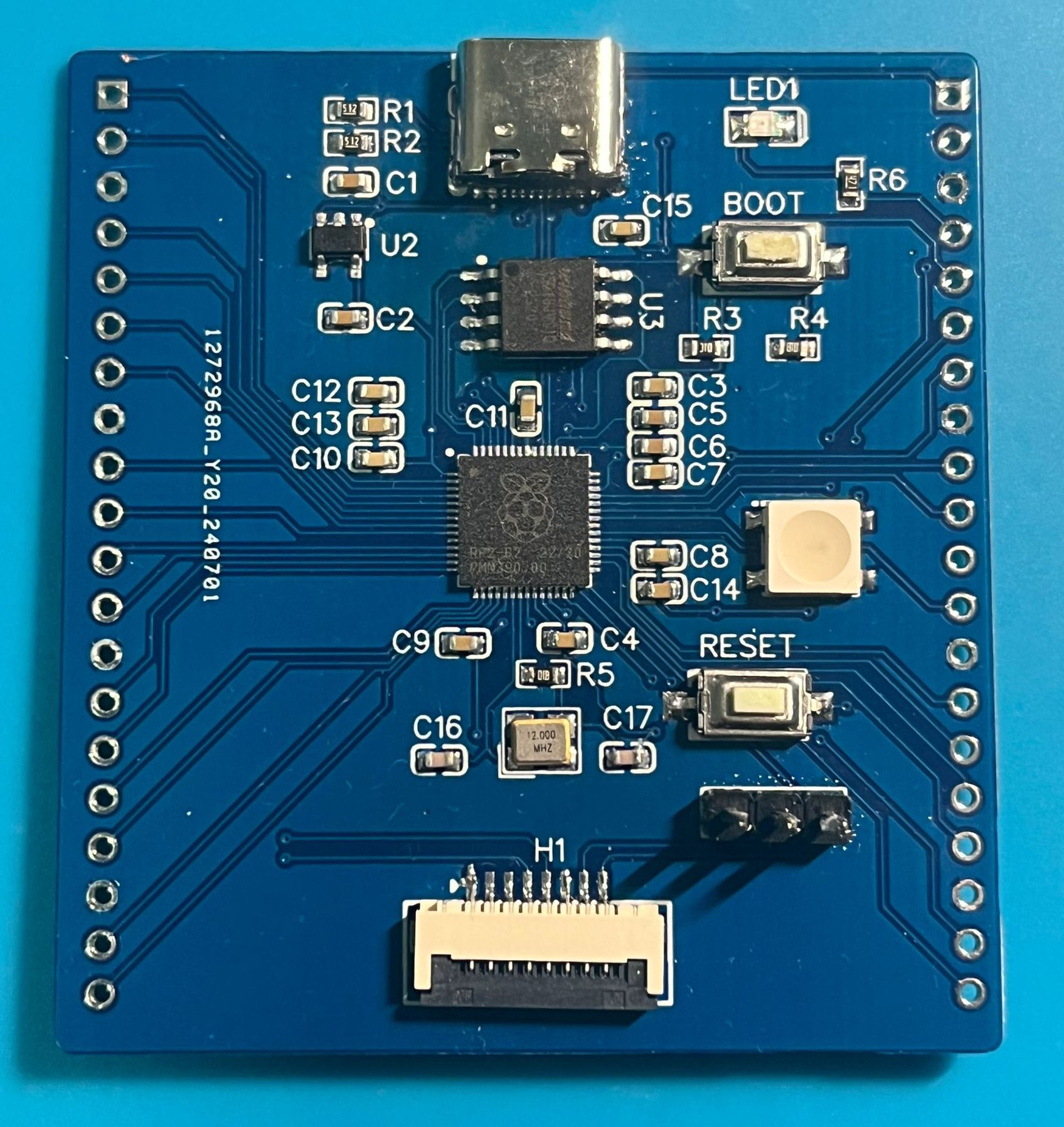

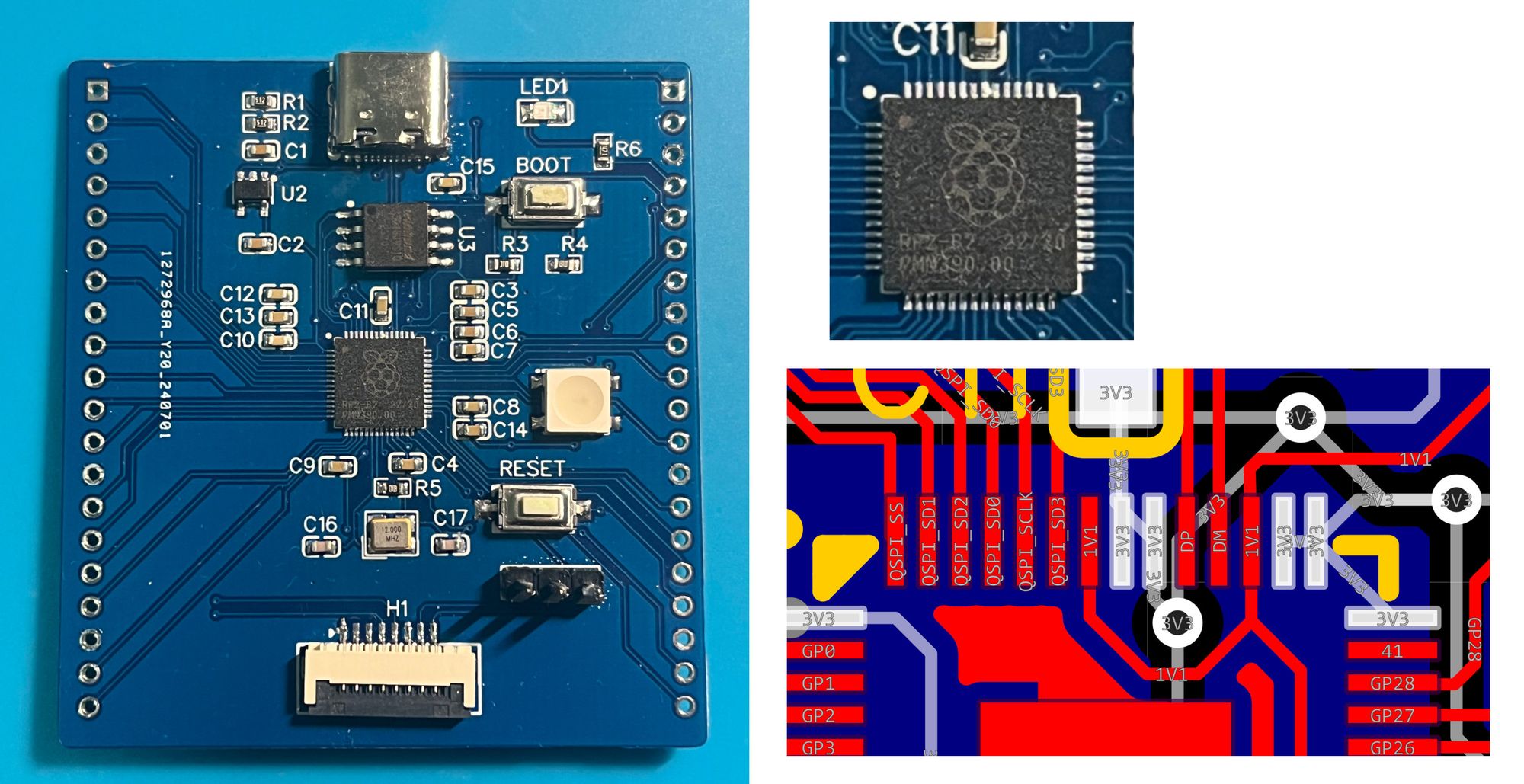

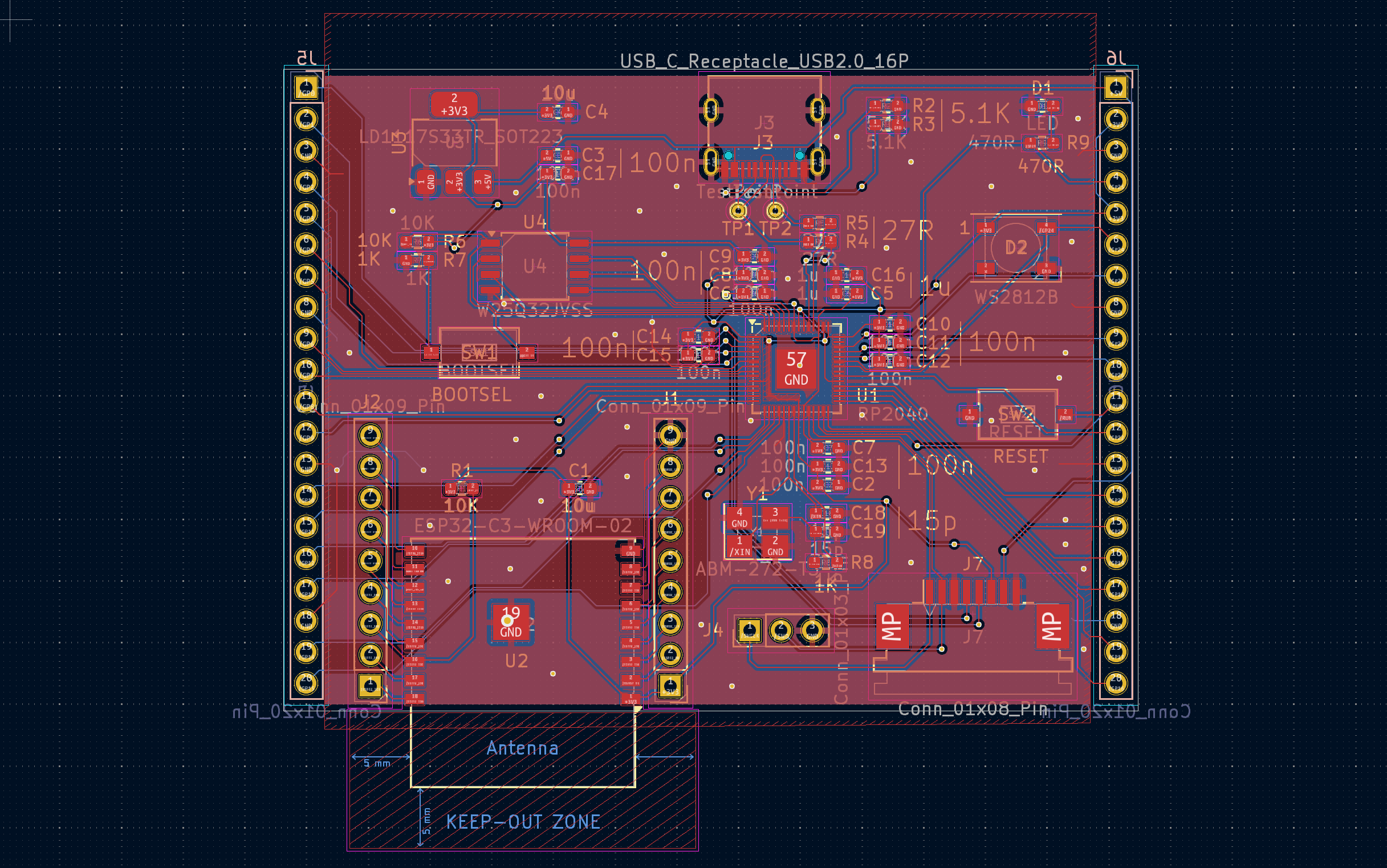

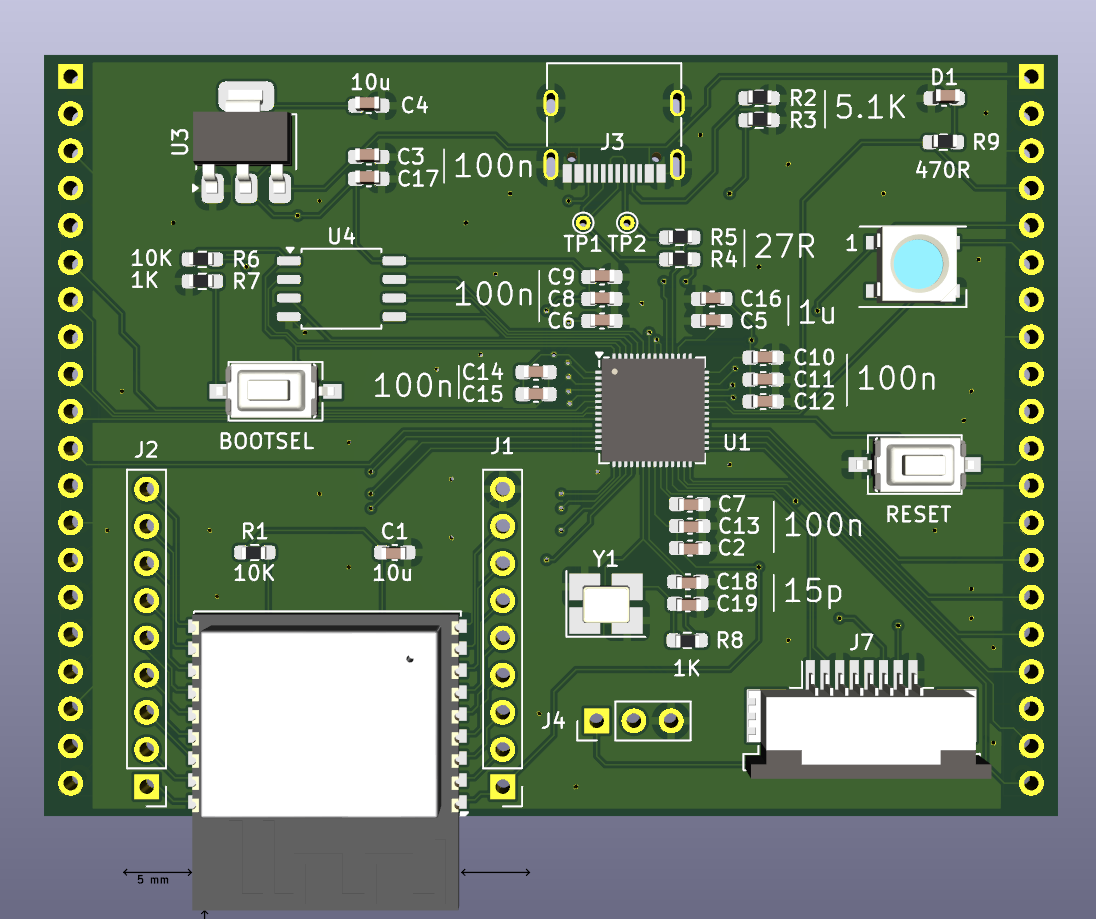

layout(画得比较难看,日后慢慢学习):

0x04 制造

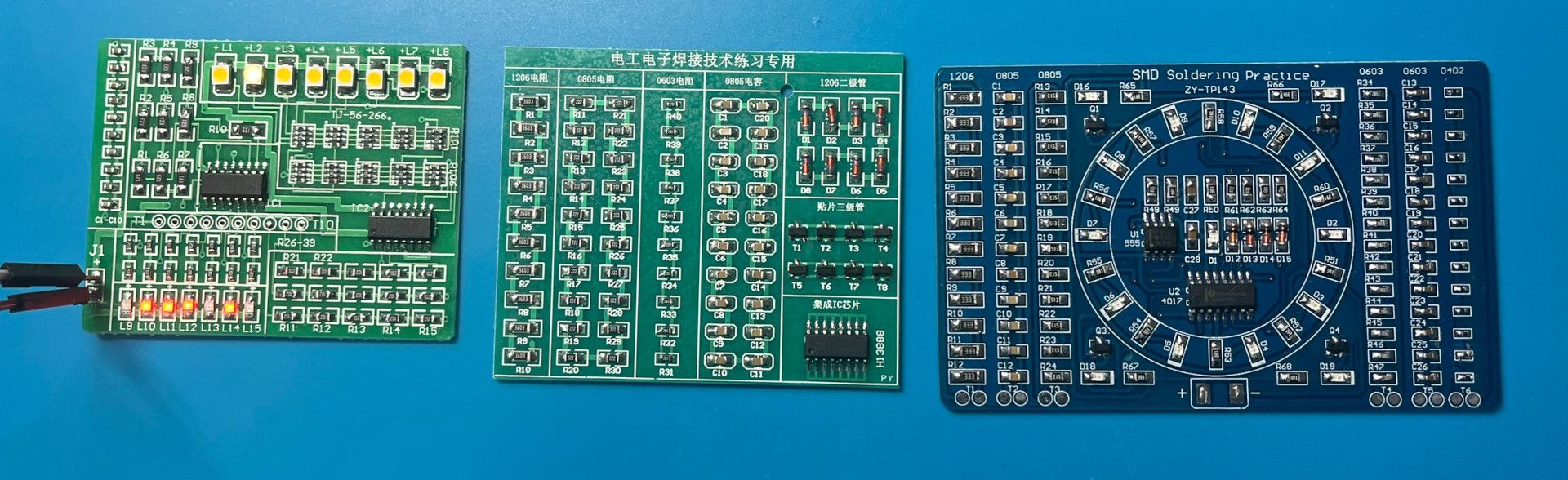

笔者在嘉立创下单了 10 张 PCB,其中 5 张贴片(只贴 RP2040 和阻容),另外 5 张用于练习手焊。等待 PCB 制造的过程中,笔者也没闲着,在家苦练焊接技术:

虽然不甚完美,但至少 0402 的阻容能完全用刀头烙铁手焊了。上文设计的 PCB,其焊接难点在于 QFN 封装的 RP2040、12 个引脚的 type c 母座、晶振,焊接时可能需要使用热风枪。

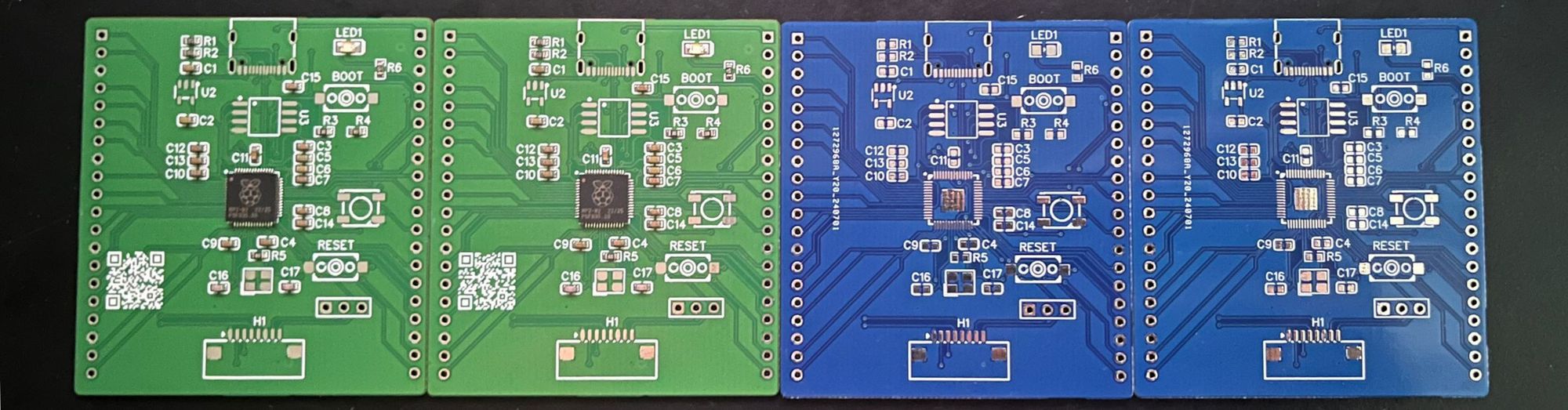

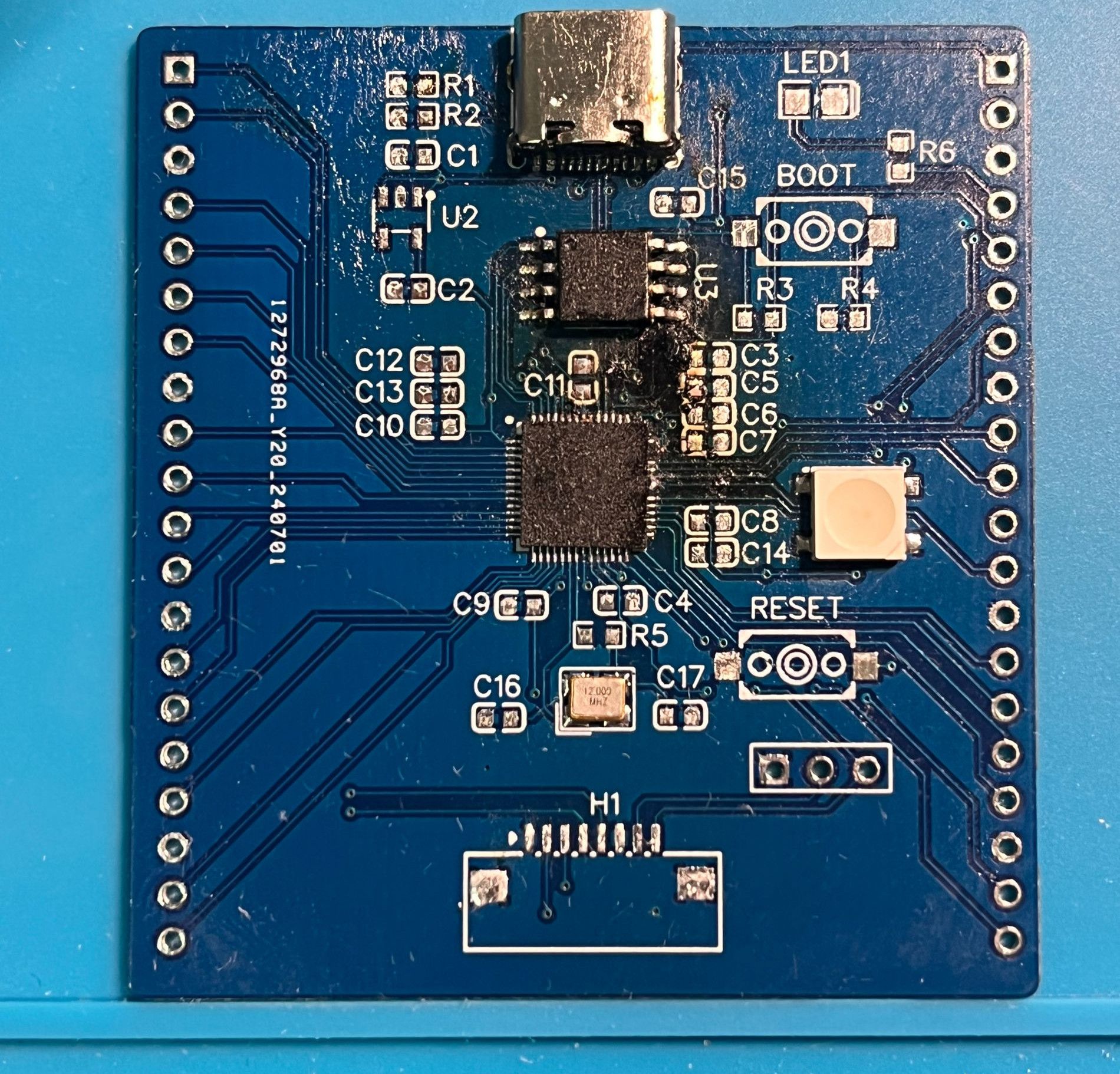

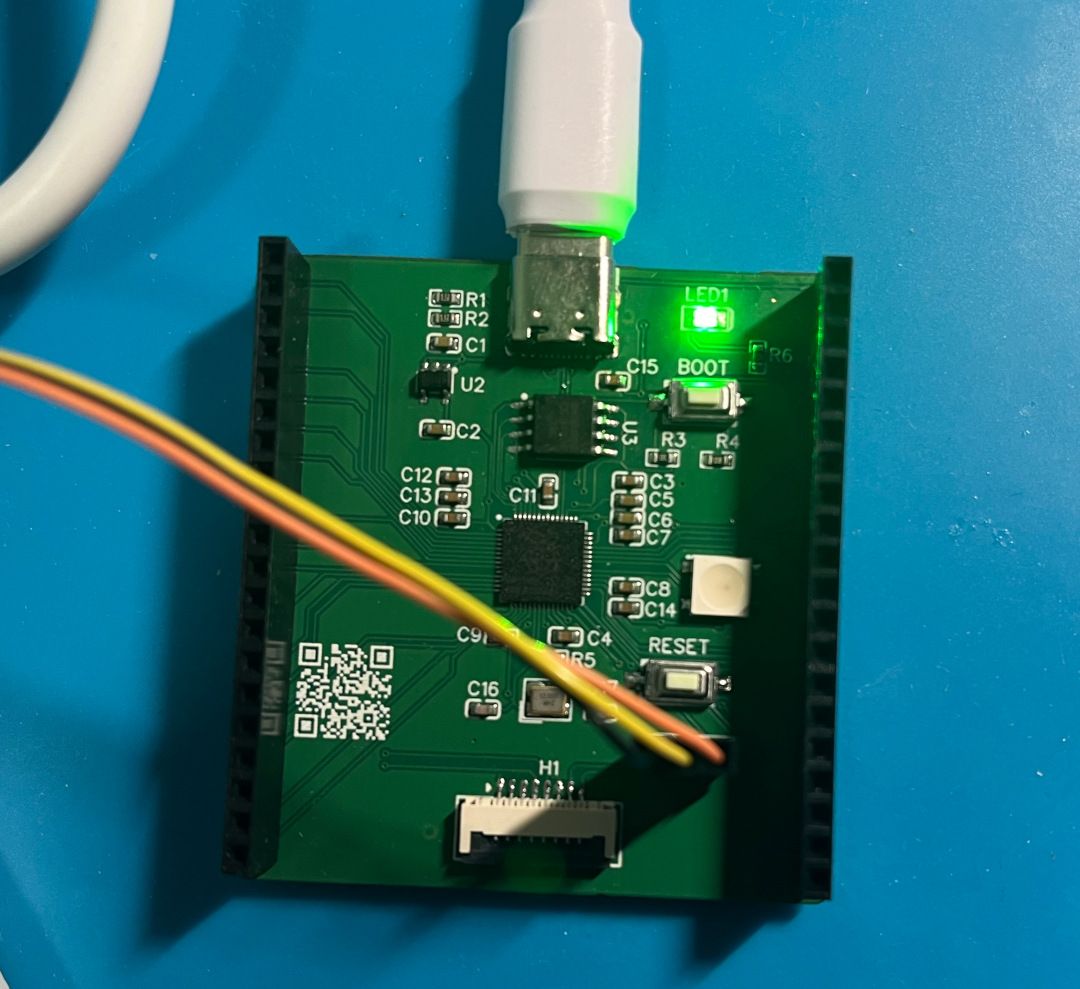

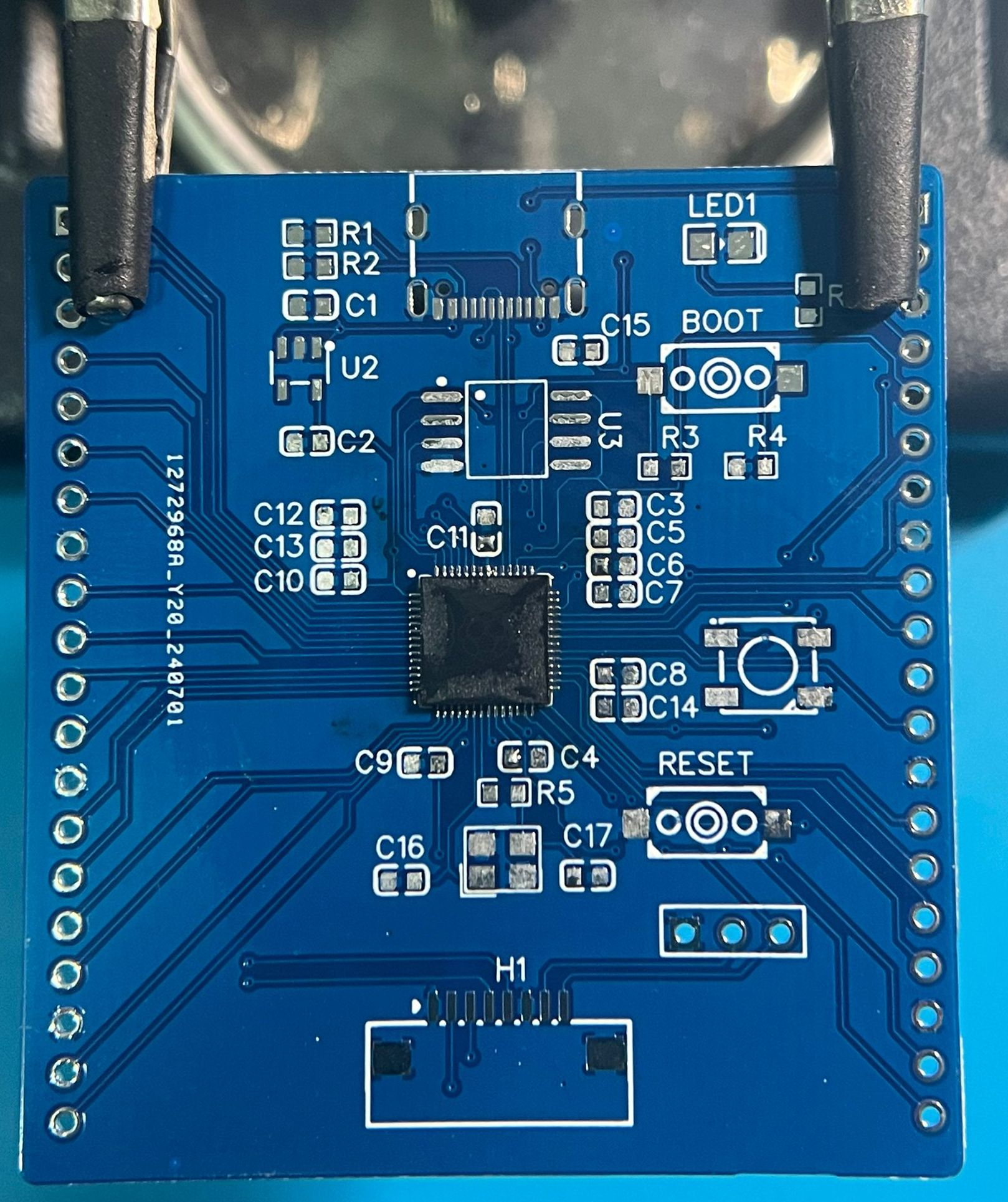

下单之后几天收到 PCB,见下图:

笔者打算先用五张未贴片的 PCB 练习手焊技术,然后把贴了片的 PCB 补焊上晶振、type c 接口等组件。

第一次尝试。t123yh 指导:给 RP2040 焊盘镀锡,中间的 EP 焊盘少上点,四周的 pin 焊盘多上点。笔者首先焊接连接器:用锡丝给 fpc 和 type c 焊盘镀锡,然后用热风枪 300 度加热,最后把塑料烧烂了。接着焊接 RP2040,不慎给 EP 焊盘上多了锡,最终未能归位,另外,风枪烧黑了 PCB 板。WS2812、flash 和晶振焊接正常。结果如下:

t123yh 指出,应当首先焊接 IC;塑料不宜被热风枪吹,而应当最后用烙铁焊接(fpc 座子可以用风枪从 PCB 背面吹)。因此,笔者在第二次尝试中做了如下改进:

- 先焊接 RP2040;

- 只给 EP 焊盘上微量锡;

- 维修佬 CMOV-559TC-HF 助焊剂似乎挥发太快了,且被风枪烧成了黑色固体。本次改用维修佬 UV11 助焊剂。

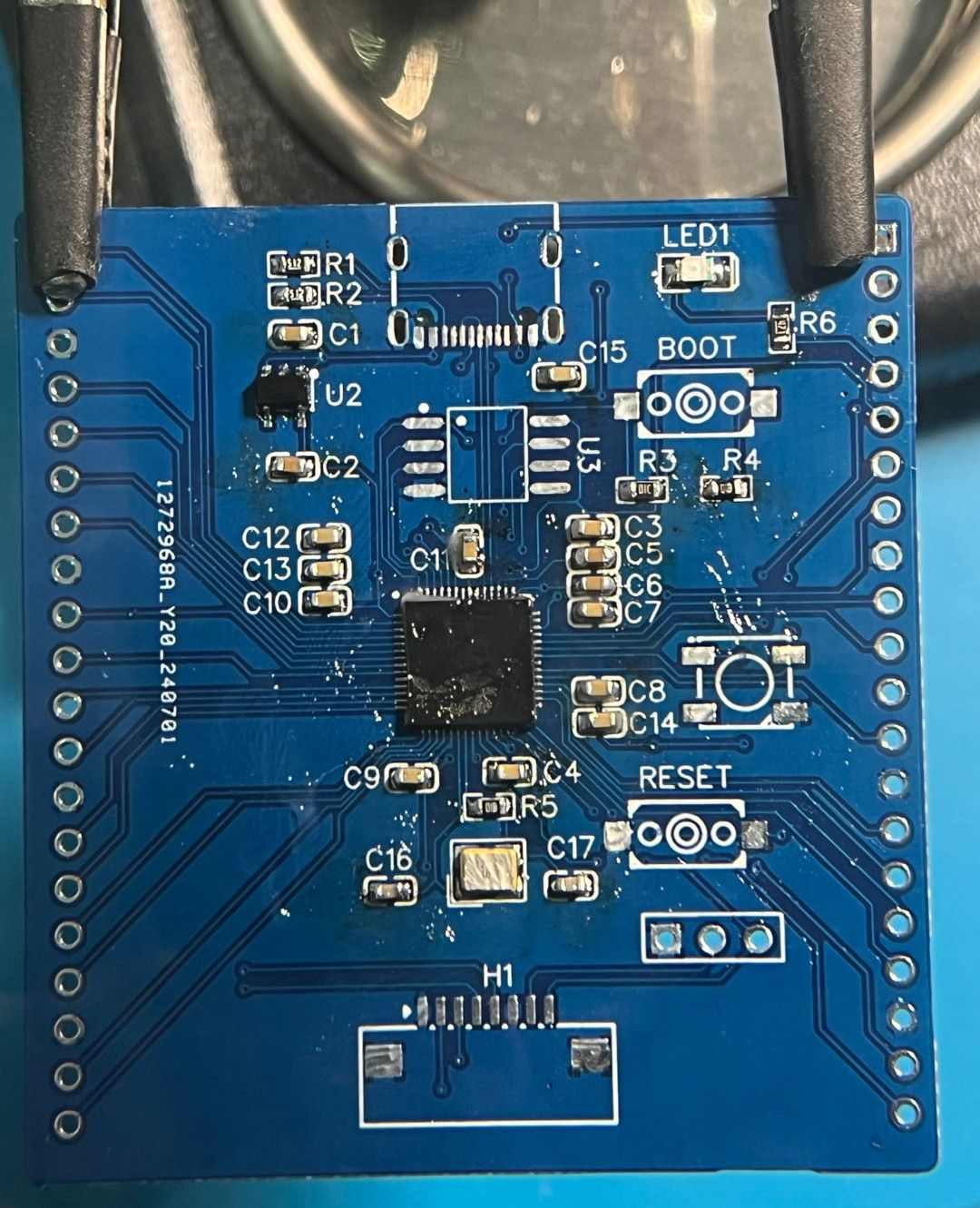

第二次尝试。应用以上改进后,结果较好。首先是没有产生大量助焊剂烟雾;其次,肉眼未观察到 RP2040 的明显问题。如下图:

然而,虽然肉眼未见异常,使用万能表可以测出有一些电阻虚焊。修复之后,连接电脑,RP2040 未正常工作。

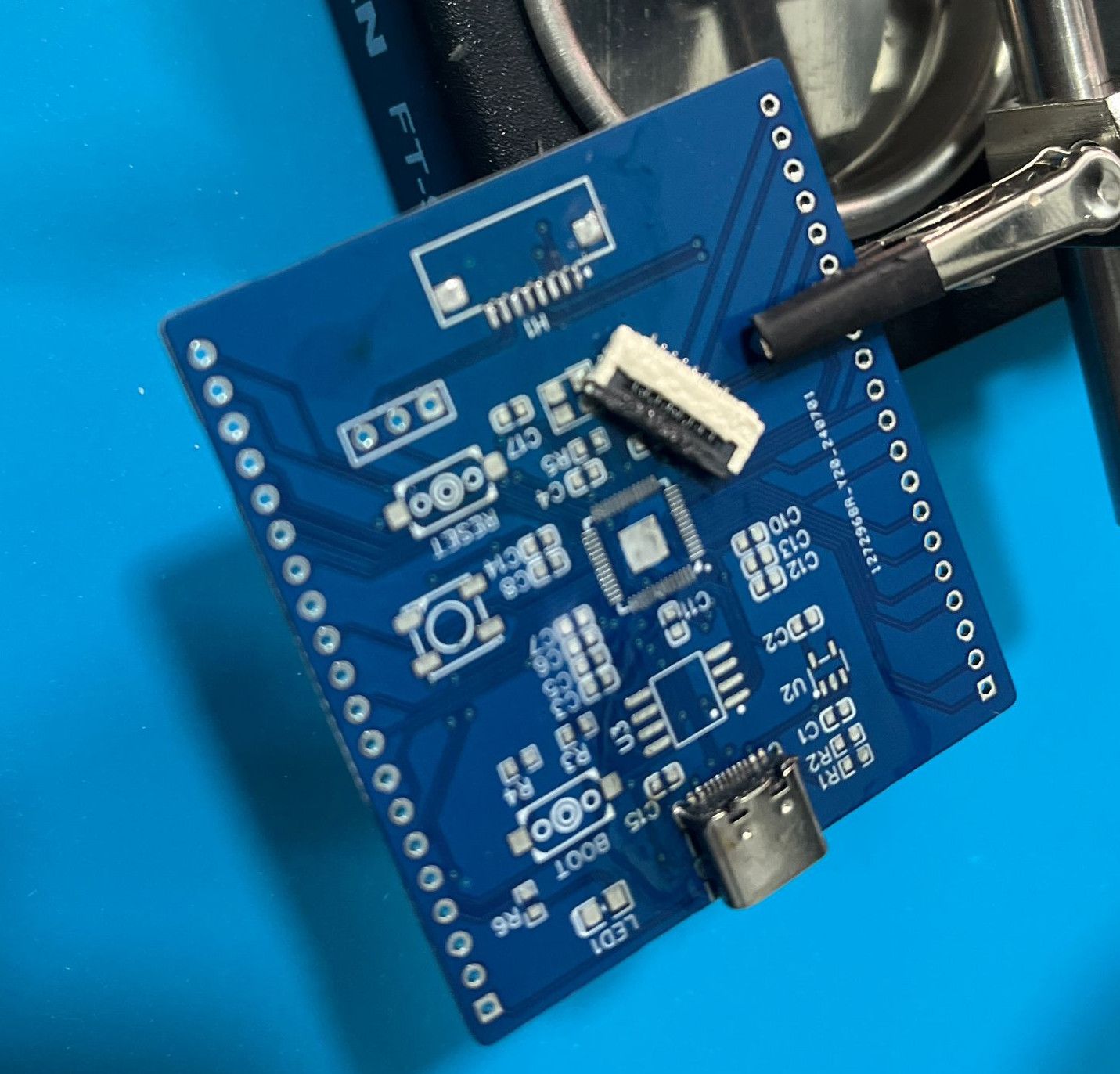

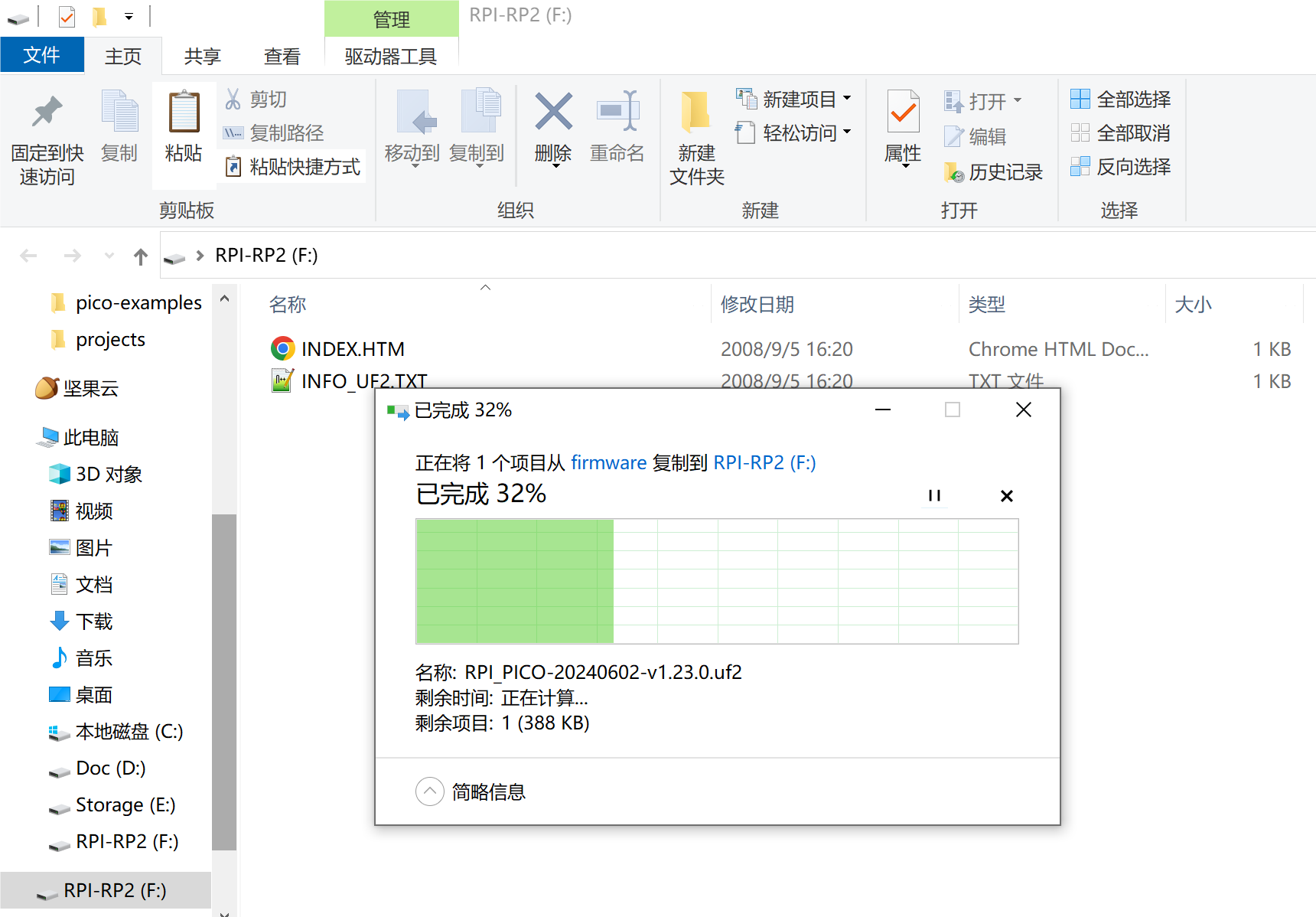

第三次尝试。考虑到现在已经有把握成功焊接 type c、晶振等元件,笔者决定本次在 SMT 板(已焊好 RP2040 和阻容)上焊接缺失的部件,以验证 PCB 设计的正确性。结果如下图。

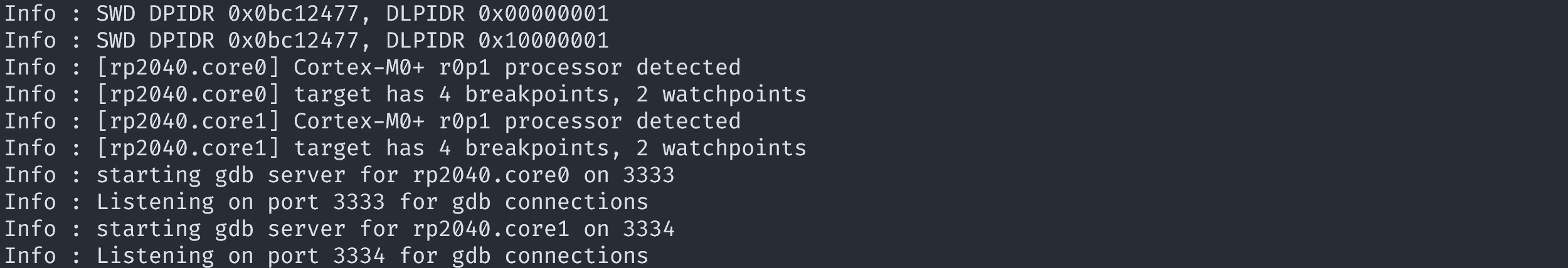

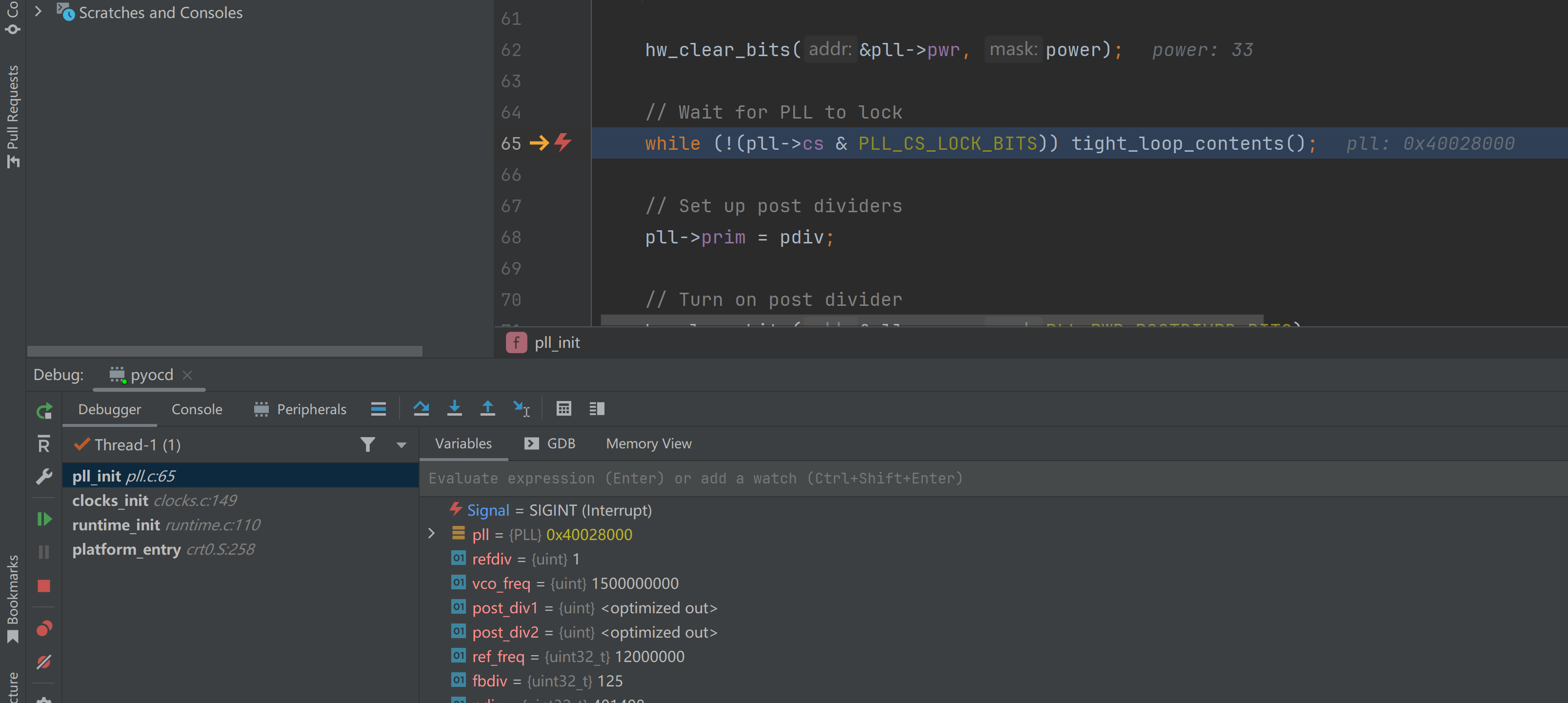

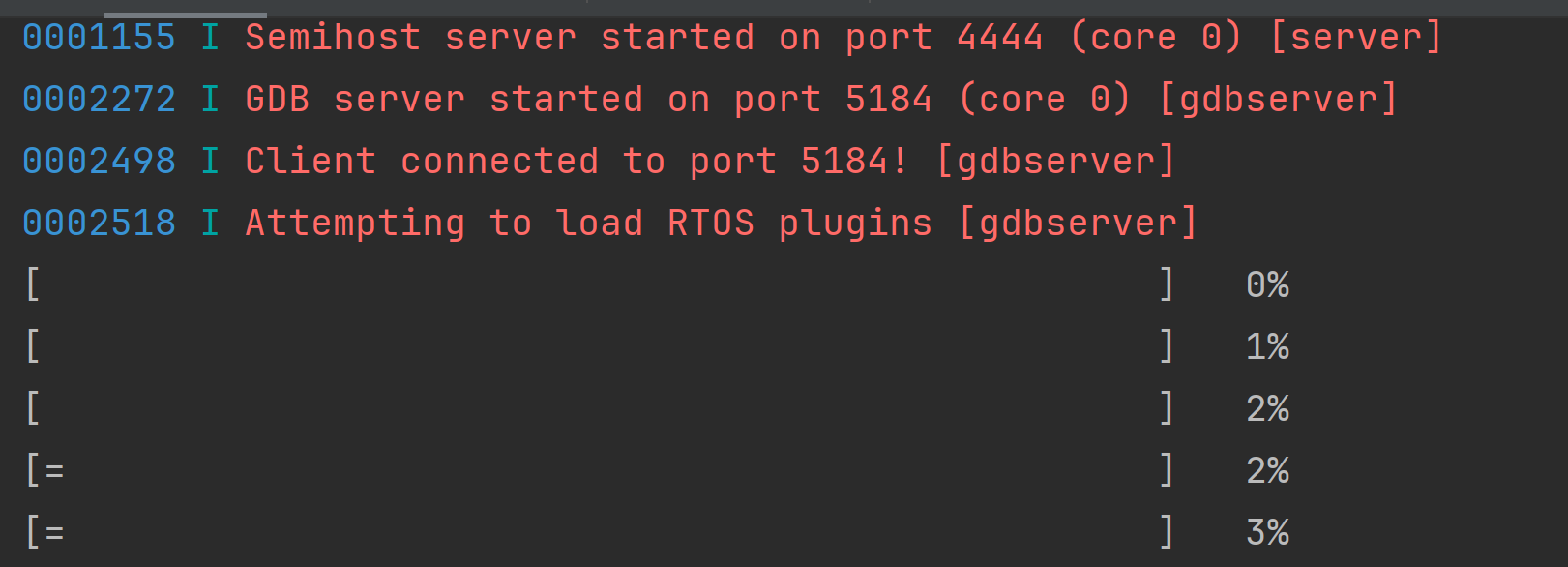

上机测试一下。虽然虚拟 u 盘仍然不工作,但是我们能通过 swd 连接到 RP2040:

然而,还是出了一些问题。烧录程序之后,发现 bootloader 卡在 PLL 相关逻辑:

这大概是晶振未焊好引起的。因此,我们下次焊接的改进点是注意晶振。另外,发现了几个 PCB 设计的问题:

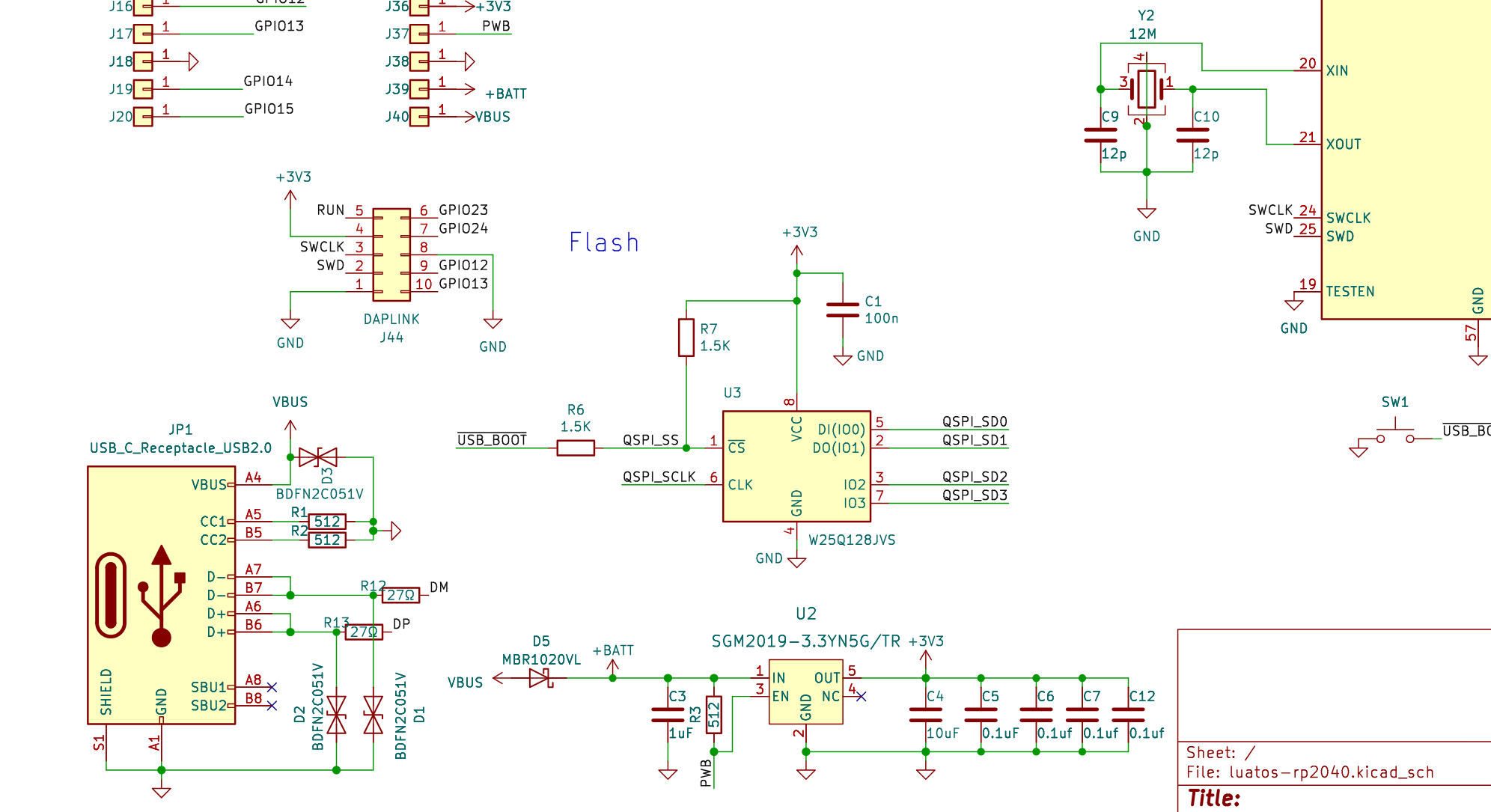

- usb 的 DP、DM 信号忘记串联 27ohm 电阻了。这可能是 usb 不识别的原因。

- 大面积铺铜导致 GND 引脚升温慢,这个问题在用烙铁焊接时尤为明显。

第四次尝试。本次焊接仍然在 SMT 板的基础上进行,与第三次尝试的不同之处在于:晶振、flash 和 LDO 采用热风枪焊接。结果成功点亮。这是本文点亮的第一块开发板。

WS2812 也可用:

现在笔者确信自己可以成功焊接除 RP2040 和阻容以外的元件。其中晶振、flash 和 LDO 采用热风枪,其他元件用烙铁。接下来,尝试在裸 PCB 板上焊接全部元件。

第五次尝试。是次焊接中,笔者按 t123yh 的建议,用风枪焊接 0603 阻容,以避免虚焊。因此,焊接流程变为:

- 用风枪焊接 RP2040、晶振、LDO、阻容、flash。焊电阻之后立即测试。

- 手焊 type c、fpc 座、按钮、LED。

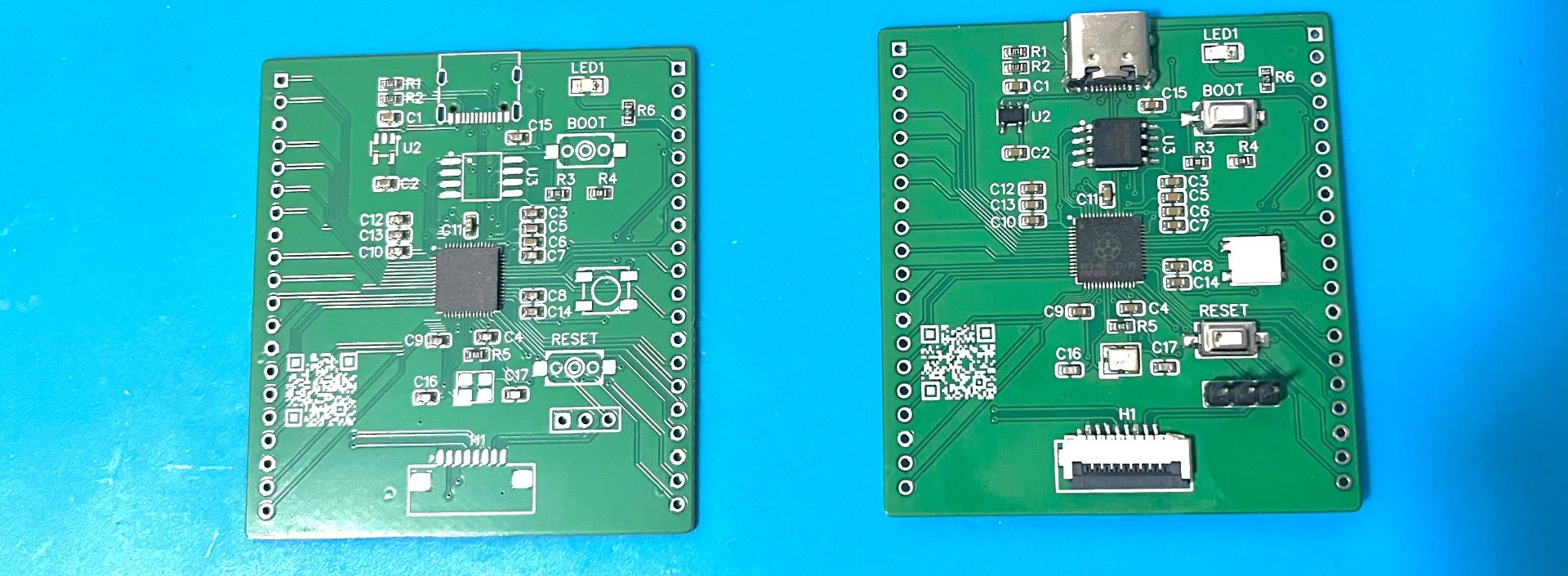

最终圆满成功:

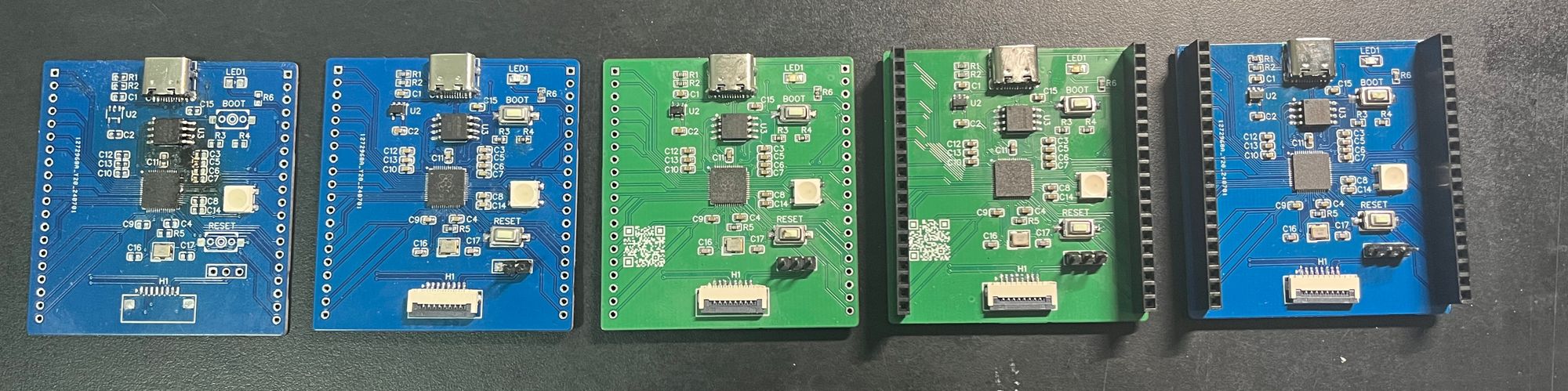

五张 PCB 的合影留念:

0x05 PCB 设计改进

下次再设计 RP2040 电路时,需要考虑几个问题:

- usb 信号需要串联匹配电阻

- 改善 RP2040 附近的走线方式

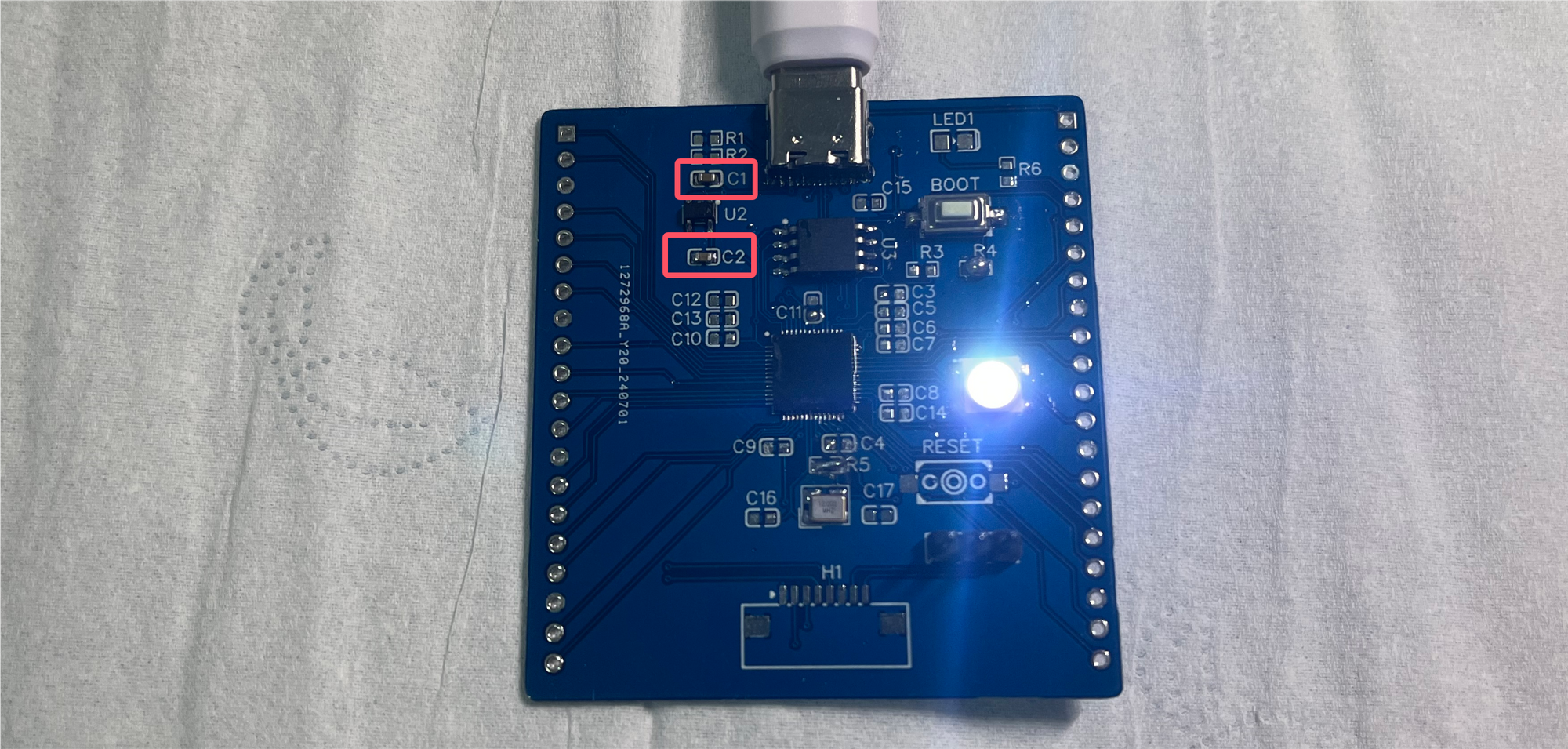

事实上,第五次尝试中,RP2040 有两个相邻引脚短路,不过由于它们都是 3V3,故未产生后果。实物如下:

日后设计 PCB 时,元件引脚应该走直线引出。上图这样的连接方式会严重影响焊接。

0x06 再次设计 PCB

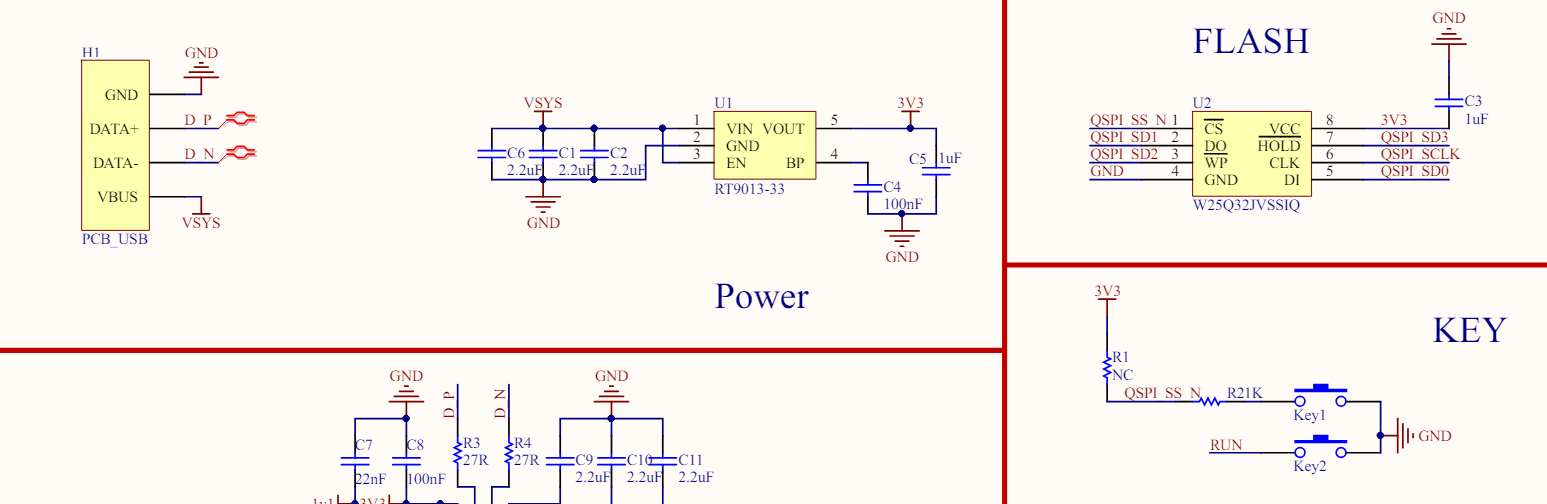

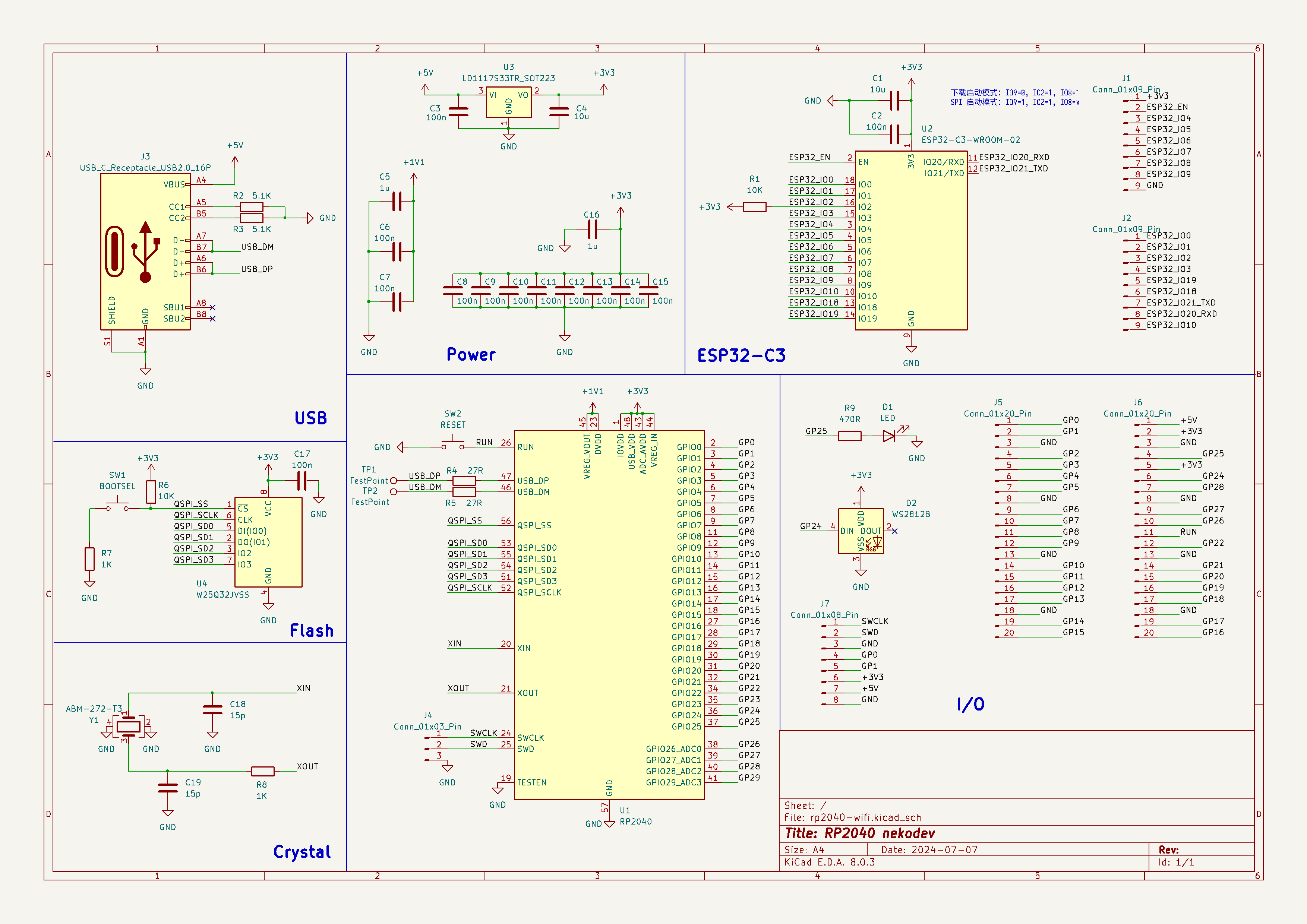

现在来解决 usb 不识别的问题,给 DP、DM 各串联 27ohm 电阻。另外,在开发板上搭载 ESP32-C3-WROOM-02 模块。

注意到该 ESP32 模块的峰值电流大约有 350mA,而 RP2040 本身需要 100mA,共计 450mA,接近 RT9013 能提供的 500mA 电流上限,故 LDO 改用意法半导体的 LD1117。LD1117 能提供 800mA 电流,且相较于 AMS1117,无需钽电容,只需在输入端并联 100nF、输出端并联 10uF 陶瓷电容。

用 kicad 设计,原理图如下:

layout:

swd、usb、ESP32 均正常运行:

0x07 后记(7 月 18 日)

后来,笔者发现第一个 pcb 其实可以正常使用 usb,27 ohm 电阻不是必须的。文中的两块开发板无法使用 usb,可能是 type c 接口焊接问题所致。

为尽量减少器件数目,笔者进行了一些测试。简而言之,如果只是想要获得一块「能跑起来」的开发板,则可以对电路进行如下精简:

- flash 方面。上拉电阻和下拉电阻均可以省略,RUN 引脚直接连到一端接地的按钮即可。滤波电容可省略。

- usb 方面。两个 27ohm 电阻可以省略,如果不使用 C-C 供电,则 CC 信号可以悬空,省略两个 5.1k 电阻。

- 晶振方面。两个电容和防过驱电阻均可省略。

- RP2040 和 LDO 方面。极限实验中,仅保留一颗 3V3 到 GND 的 1uF 电容,摘掉所有其他电容,仍然可以正常工作。

下图中的电路板是可以正常工作的。只保留了 LDO 的输入滤波和输出滤波电容。

一些调试经验:

- RP2040 上电后,电流大约是 10 ~ 30 mA。

- 一旦 RP2040 上电,即可使用 SWD 连接上内核,无需晶振和 flash。这可以用于判断 RP2040 是否焊好。

- usb 下载模式电流大约 15 mA。

- 如果电脑上弹出了虚拟 u 盘,说明 RP2040 和晶振正常工作;进一步地,如果可以下载成功,说明 flash 正常工作。

- 另一种判断晶振是否正常的方法:用万用表测量 XIN 或 XOUT 的对地电压,约为 1.5V。

- 不要直接使用

pyocd gdb指令来连接 RP2040,会弹出「No cores were discovered」,然后需要复位 RP2040 才能重新连接。应该使用pyocd gdb -t rp2040或使用 openocd。

焊接步骤:

- 焊接 RP2040、type c 和 swd 接口,用 debug probe 连接上内核,说明 RP2040 焊接良好。

- 焊接晶振,上电后弹出虚拟 u 盘,说明晶振焊接良好。

- 焊接 flash,虚拟 u 盘可以正常下载,说明 flash 焊接良好。

0x09 后记(8 月 1 日)

本文的焊接过程编写于 7 月 5~6 日。今天是 8 月 1 日,回顾一个月前磕磕绊绊的焊接过程,感慨万千。笔者在六月初的第一篇 RP2040 文章中写道:

RP2040 芯片采用 QFN-56 封装,焊接是个问题。笔者焊个 0603 封装的电阻尚且费劲,去年焊 UFQFPN-20 封装的 STM8S003F3U6 时,失败率更是高达 100%。有两条解决方案:要么购买邮票孔开发板当作模块使用,要么苦练焊接技术(加热台和热风枪可以降低焊接难度)。笔者打算先用手上的开发板学一段时间,等到设计 PCB 之后,再练一练焊接技术,争取能够手焊。

笔者在学习 RP2040 之前,焊功的确是很差的。直插元件当然谁都会焊,1206 电阻也不困难,0603 则略显吃力:这就是笔者一个月前的水平。在过去的一个月间,笔者画了 10 块 PCB(同时从立创 EDA 切换到了 KiCad),焊了几十块板子,有些熟能生巧的感觉了。如本文所述,笔者在 7 月上旬学会了焊接 RP2040,那时需要大量使用助焊剂;而今天笔者可以在不使用热风枪、不添加助焊剂的情况下,仅用烙铁焊接 RP2040。

笔者学习焊接的过程,很像高一时学习动态规划(DP)的过程。它们本身的原理并不复杂,但简中互联网上缺乏合理的教材,导致学习曲线比较陡峭。B 站上的所谓「焊接教程」大多是一分钟的短片,拍摄一段焊接过程,毫无分析,看完之后也云里雾里。掌握一些技能之后,回望自己的学习经历,令人哭笑不得。今天也该写一点焊接学习笔记,以期帮助到有需求的读者。

PCB 焊接中,存在如下现象:

- 在助焊剂充足的情况下,锡拥有很强的流动性,性质与水类似;若锡失去流动性(体现为拉丝或难以熔化),则补充助焊剂可以恢复其流动性。少量的助焊剂即可让锡拥有较好的流动性。

- 锡丝中自带助焊剂,但助焊剂会随着加热而蒸发,烙铁温度越高,助焊剂蒸发越快。烙铁刚接触锡时,锡的流动性很好,过几十秒钟之后流动性很差,即是助焊剂蒸发的结果。

- 在助焊剂充足的情况下,烙铁很容易沾锡。利用这个特性,我们可以用烙铁去除焊盘上多余的锡。引脚之间的连锡有时也可以通过此方法清理,即把烙铁用海绵擦干后,接触连锡的部位,带走一点锡,重复操作。

- 吸锡带可以用于清理难以用烙铁吸走的锡,但它仅在助焊剂充足的情况下正常工作。

- 不同焊盘上的锡,熔化速度不一样,这是正常现象。连接到大片铜的焊盘散热很快,因此 GND 焊盘一般熔锡较慢。但不宜贸然调高烙铁温度,因为容易让助焊剂快速蒸发,导致焊接更加困难。

- 助焊剂除了去除氧化层这一作用以外,还能传导热量。

由此可见,焊接中绝大部分的问题都可以用助焊剂解决,所以笔者建议初学者总是使用过量的助焊剂(不时用小刷子把助焊剂涂到焊盘周围),焊接完成后再用洗板水清理。

另外,简单讨论一下如何不使用风枪或加热台、不额外添加助焊剂,仅用烙铁和锡丝完成一些元件的焊接。这个过程最重要的任务是助焊剂管理,需要时刻观察烙铁头和焊盘上的助焊剂余量。助焊剂的唯一来源是锡丝内芯,所以缺乏助焊剂时,只能通过上锡来补充。

- 直插类元件。注意加热焊盘而不是锡丝,从而锡可以完整包裹焊盘,而不是挂在引脚上形成水滴状。

- LQFP / SOP 等封装的元件,例如 STM32F103CBT6。焊接这类元件时,可以把机械连接和电气连接分开考虑。首先选一个位于角落的焊盘,将其上锡并熔化,把元件摆好,等锡凝固,形成机械连接。由于元件已被固定,焊接其他面的引脚便十分轻松,无需担心烙铁触动元件。在其它面焊接完毕后,再焊接最初用于机械连接的那个面。

- QFN / UFQFPN 等封装的元件,例如 RP2040、STM32G031G8U6。先给烙铁上锡,然后左手用镊子把元件摆正,右手用烙铁在一个面上反复拖动。由于助焊剂业已蒸发殆尽,拖动几次之后,这个面上就会有很不规整的锡(充满了连锡和虚焊),不过没关系,此步骤只需要建立机械连接,不考虑电气连接。接下来,焊接其他三个面,步骤是先给烙铁上少量锡,然后在被焊接的面上从上往下拖焊。若肉眼观察到整齐的反光,则说明焊接良好;否则重新从上往下拖焊。若助焊剂耗尽,则在海绵上擦干烙铁,重新上一点锡,获得新锡丝中的助焊剂。三个面焊接好后,回头处理最初用于机械连接的面,用烙铁吸走那些锡,然后焊接方法与其它面一致。需要注意,本方法无法焊接 EP 焊盘,若一定要求 EP 焊盘连接上芯片(例如 CH334P 的 EP 焊盘是唯一的 GND 接口),则要么采用热风枪,要么设计 PCB 时在 EP 焊盘上打孔,从背面焊接。

- type c 母座和 FPC 座。这类器件不宜提前上锡,因为上锡之后,各个焊盘的锡高度不一致,最高的焊盘会把元件顶起来,使得其他焊盘的锡难以连接引脚,且即使焊接成功,也会降低机械强度。我们应当让所有引脚紧贴焊盘,方案有二:一是不使用锡丝上锡,而是用锡膏覆盖焊盘,这样引脚自然可以紧贴焊盘,用烙铁头拖一遍给锡膏加热,即可焊好。缺点在于,若没有钢网,容易把锡膏涂得到处都是,加热后可能产生许多小锡珠。另一个方案与 QFN 的思路类似,先给烙铁上锡,然后用镊子压紧座子,用烙铁在一侧引脚上拖动,形成机械连接,固定四五个引脚。然后去焊接另一侧的引脚,缓慢拖焊。一路拖焊回来之后,其他引脚已经形成了可靠的机械连接,所以可以去除原先用于固定座子的锡,继续拖焊即可完成焊接。

参考工具:T12 焊台(雪驹电子)、KU 或 SK 小型刀头(维修佬)、0.8mm Sn63PbA 锡丝(友邦)。